博通推出配置CPO的下一代交换ASIC

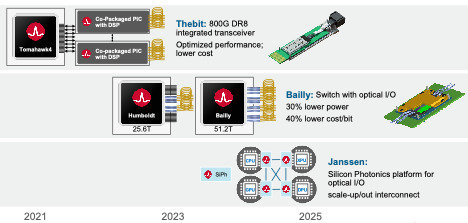

ICC讯(编译:Nina)据LightCounting(LC)报道,这是官方消息。2021年1月12日,博通(Broadcom)推出了一系列配置了共封装光学器件(co-packaged optics)的下一代交换ASIC。如下图所示,第一款25.6Tb Humboldt将于2022年底上市,而51.2T Bailly将再等一年。博通还推出了800G DR8可插拔收发器,该收发器基于与DSP共同封装的硅光子集成电路(PIC),以及未来将光学元件与CPU和GPU共同封装的计划。

博通很少在可以出货前就发布新品,这次是一个特例。客户需要时间来接受变化。这一消息对于博通最大的客户来说并不意外,但对于需要参与进来的更广泛的市场来说却是一个意外。比赛的号角吹响了,竞争已经开始,博通计划继续保持领先地位。

LC对此也并不感到惊讶。在2020年12月发布的共同封装光学预测中,该调研公司曾预计2021年将有相关新品发布。未来可能还会有更多。

为什么从25Tb开始?业界共识是,102Tb交换机需要共封装光学,可能51Tb交换机也需要。博通开始得更早,让客户有更多时间来研究和尝试新技术。但是,即使25T CPO解决方案也有可能实现规模部署,因为它将在成本和功耗方面带来巨大优势。

在COBO、CPO和OIF的概念中,共同封装光学元件带有电气和光学连接器。博通的方法将光电芯片焊接在ASIC旁边(在同一基板上)。光纤可能仍然是可拆卸的,但博通没有提供有关其实现方法的任何细节,除了表示每个芯片64个I/O光纤,带宽密度为500Gbsp/mm。

这是一个面向未来的设计。小芯片(Chiplet)上专为100Gbps通道速度设计的electrical socket的丢失虽令人头疼,但提高速度将是一个噩梦。博通的方法可以减少电力损耗,并通过集成到ASIC中的标准LR SerDes来直接驱动光电小芯片,这是“整个系统中硅的最有效利用”。

这次发布还表明博通完全拥有配备CPO的ASIC。如果需要更换,请拔掉光纤的插头并卸下整个ASIC。CPO由外部激光器供电,以提高可靠性。激光器作为前端可插拔模块来使用,就像今天的收发器一样。它实际上是为习惯于插入光学器件并根据需要更换的客户设计的。

博通的客户还将欣赏到,光电芯片将与光收发器MSA(如DR4和DR8)兼容。这将使CPO和可插拔收发器在大型数据中心中共存。

本文地址:http://www.iccsz.com//Site/CN/News/2021/01/22/20210122030206561347.htm 转载请保留文章出处

关键字: 博通 CPO

文章标题:博通推出配置CPO的下一代交换ASIC

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1