基于45 nm CMOS工艺的硅基光电融合单片集成光互连芯片

1、工作简介

伴随人工智能、机器学习和高性能计算等新一代信息技术的迅猛进步,数据搬移对互连的宽带和能效需求指数型提升。电互连受限于导线损耗和微电子工艺演进,难以满足未来超高带宽、百米距离扁平化网络连接的需求。硅基光互连技术利用CMOS成熟节点工艺制备集成光路与电路,在计算芯片封装内构建光输入/输出接口(optical I/O),极大地延伸了芯片间低延时数据互连,为构建大容量数据传输的高能效、大规模并行计算系统奠定了坚实基础。

与传统网络通信不同,计算互连要求极高的带宽密度、能耗效率与极低的延时,这决定了其并行多通道的系统架构,以及无DSP辅助下超低误码率(BER<10-12)的需求。但值得注意的是,基于分立光电子芯片的封装集成不仅限制了芯片规模,还在关键性能方面造成显著恶化:封装键合引入的寄生损害了信号完整性,高频信号进出芯片增加了不必要的功耗。硅基光电融合单片集成技术,在硅衬底上将光器件与电路一体化设计和单芯片制备,可打破互连带宽和能效的固有瓶颈,显著降低封装复杂性并降低收发功耗,被认为是推动人工智能、高性能计算和数据中心网络可持续发展的核心支撑技术。

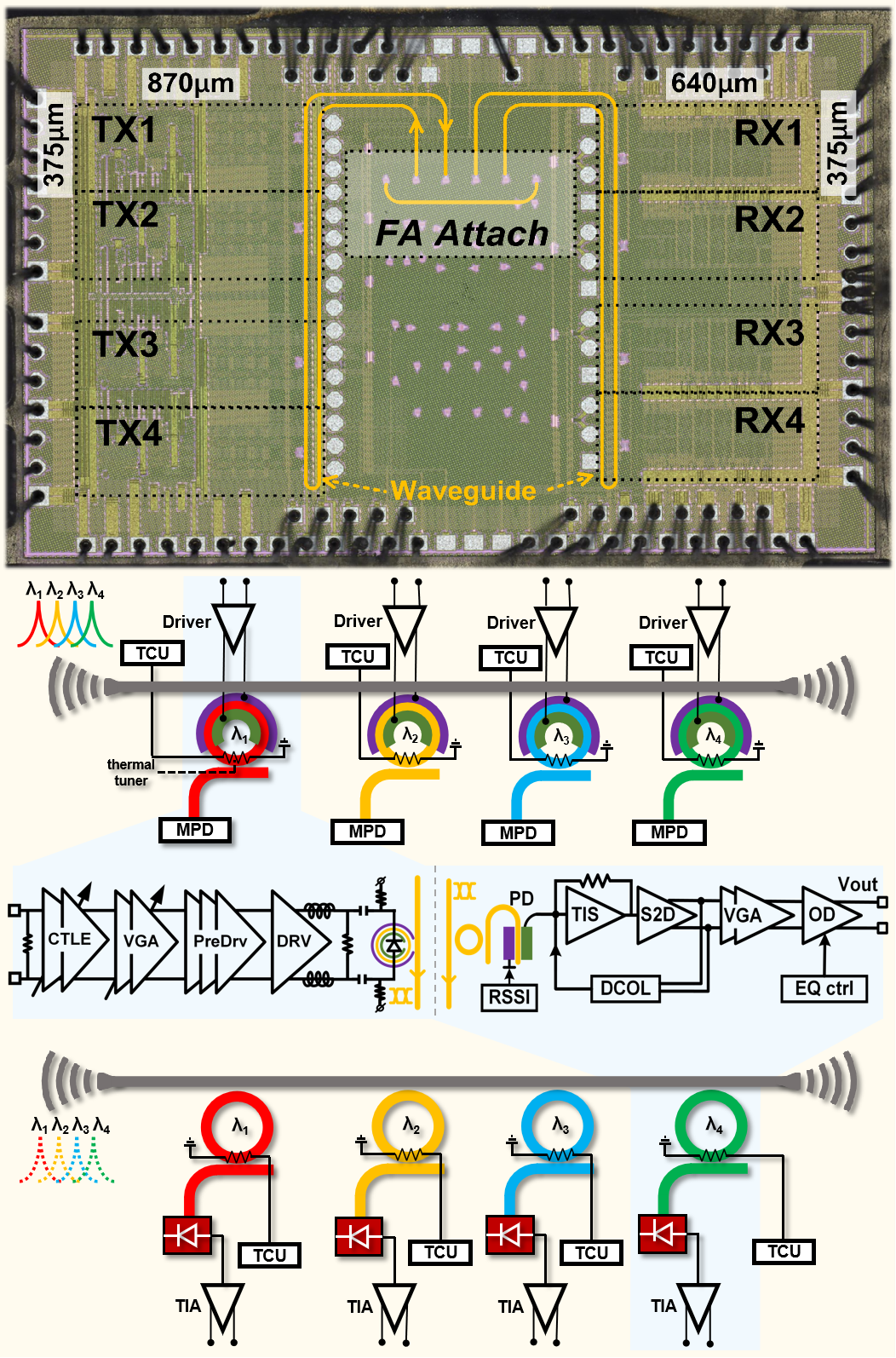

中国科学院半导体研究所李明研究员团队与祁楠研究员团队合作研制出国内首款基于45 nm CMOS工艺的硅基光电融合单片集成光互连芯片,成功实现了光电子与微电子等器件的单片融合集成,单通道支持64 Gb/s传输速率,借助微环谐振波分复用技术,4通道单向总带宽达到256 Gb/s。图1显示了该硅基光电融合单片集成光互连芯片,单片集成了微环调制器、微环滤波器、热相移器和光电探测器等光学器件,以及驱动器和跨阻放大器等电学器件。

图 1. 硅基光电融合单片集成光互连芯片实物图及系统框图。

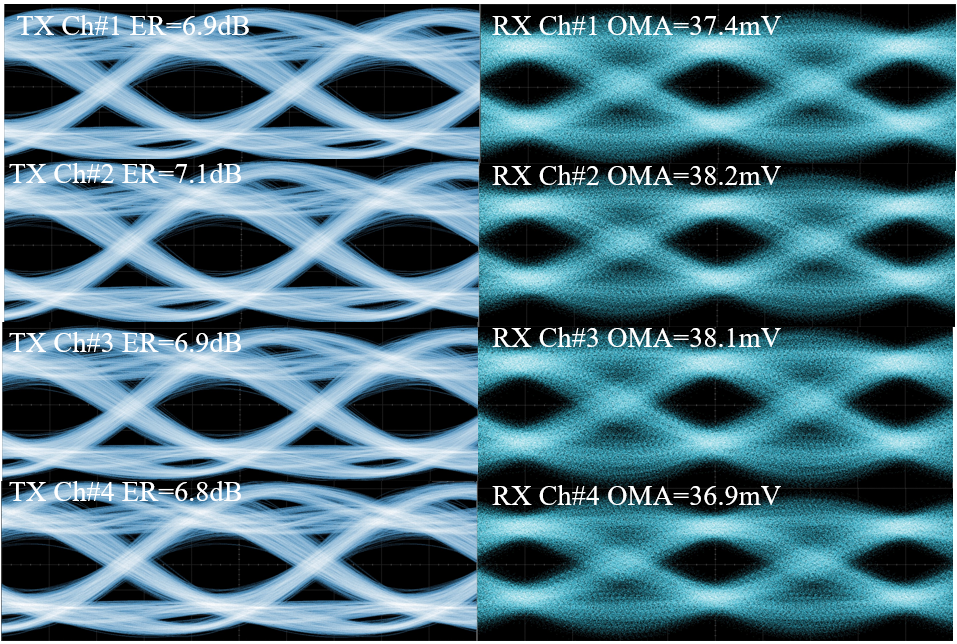

图2为芯片封装测试实物图,图3为大信号测试结果,单通道光收发芯片均可以实现清晰的64 Gb/s眼图信号传输,收发芯片总能效达到2.85 pJ/bit,比特误码率可达到10-12以下。

图 2. 芯片测试板实物图。

图 3. 4通道发射机和接收机的眼图,单通道速率为64 Gb/s NRZ。

图4展示了本项工作与国际代表性成果的对比,其中与光电单片集成技术国际领先的Ayar Labs公司2024年报导结果相比,本文实测单通道速率由32 Gb/s提升至64 Gb/s,具备更高的收发能耗效率,为更多通道并行的带宽拓展提供了更好的性能前景。

图 4. 与国际相关代表性成果的性能比较。

该工作以 “A 256 Gb/s Electronic-Photonic Monolithically Integrated Transceiver in 45 nm CMOS”为题目,在Journal of Semiconductor上发表短篇通信论文,快速报导了成果与进展。

本工作得到国家自然科学基金资助:国家杰出青年基金项目(61925505),集成芯片前沿技术科学基础重大研究计划项目(92373209),重点基金项目(62235017)。

关于作者:李昂,目前于中国科学院半导体研究攻读博士学位。目前主要研究方向为硅光子学的高速光电器件和光电集成。

本文地址:http://www.iccsz.com//Site/CN/News/2024/06/19/20240619091550095443.htm 转载请保留文章出处

关键字:

文章标题:基于45 nm CMOS工艺的硅基光电融合单片集成光互连芯片

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- · Imec推出基于CMOS的56Gb/s零中频D波段波束成形发射机 具有卓越的输出功率和能效

- · 通用单元硅基光电子集成电路的全局优化

- · 喜迎新会员 | 深光谷:提供领先的光互连解决方案

- · TeraSignal推出业界首款CMOS智能Re-Driver 以改变人工智能和计算互连

- · Quintessent募集1150万美元种子基金,打造面向未来的高速光互连

- · Broadcom基于16nm CMOS工艺的600Gbps DP-QAM64相干光收发器前端设计技术解析

- · 硅基光电子技术:台积电副总经理张晓强博士在IEEE年度盛会ISSCC上的见解

- · 行业研究|光互连技术引领高性能计算进入新时代

- · 厦门优迅推出基于CMOS工艺的 10G传输应用低功耗整体解决方案

- · iFOC 2023回顾 | 京东云陈琤:光互连聚焦硅光、CPO、线性及相干光学

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1