Broadcom基于16nm CMOS工艺的600Gbps DP-QAM64相干光收发器前端设计技术解析

简介

光通信系统对更高的数据传输速率的需求不断增长,推动了对先进调制格式和高性能收发器的需求。要实现每波长 400Gbps 以上的数据传输速率,有前景的解决方案是采用复杂的调制方案,如双偏振正交幅度调制(DP-QAM64)。这种调制格式通过为每个符号编码更多比特来提供更高的频谱效率,从而在电气和光学信道的有限带宽内实现更高的数据传输速率。

在本教程中,我们将探讨 Broadcom 设计和实现的 600Gbps DP-QAM64 相干光收发器前端,其特点是在 16nm CMOS 工艺中采用四个同步的 105GSps 8 位模数转换器 (ADC) 和四个数模转换器 (DAC)[1]。我们将深入探讨包括模数转换器、数模转换器和锁相环 (PLL) 在内的关键构建模块,并讨论为实现高性能和高效运行而采用的创新技术。

相干光收发器概述

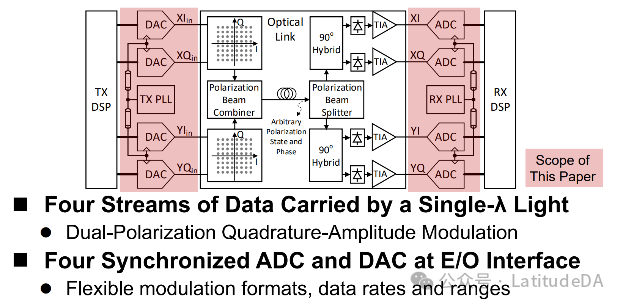

相干光收发器采用 DP-QAM 调制方案,通过单一波长的光收发数据。如图 1 所示,发射器由四个 DAC 组成,分别产生两个偏振(X 和 Y)的同相(I)和正交(Q)分量。这些信号通过偏振合束器组合并调制到光载波上。

图 1. 基于 ADC/DAC 的相干光 TRX

在接收端,利用偏振分束器和 90 度混合器将光信号分成偏振分量。由此产生的四个信号(XI、XQ、YI、YQ)通过四个 ADC 转换回电域。数字化信号由数字信号处理(DSP)模块处理,以恢复传输数据。

本文的重点是四个 ADC、四个 DAC 以及为转换器生成高速采样时钟的 PLL 的设计和实现。

ADC 设计

ADC 设计采用时间交错架构,以实现 105GSps 的目标采样率。如图 2 所示,ADC 由 192 个单元逐次逼近寄存器 (SAR) ADC 组成,这些 ADC 采用两级跟踪保持 (T/H) 电路进行时间交错。输入信号首先由集成了失真消除电路的可变增益放大器 (VGA) 放大,以获得高线性度。

图 2. ADC 框图

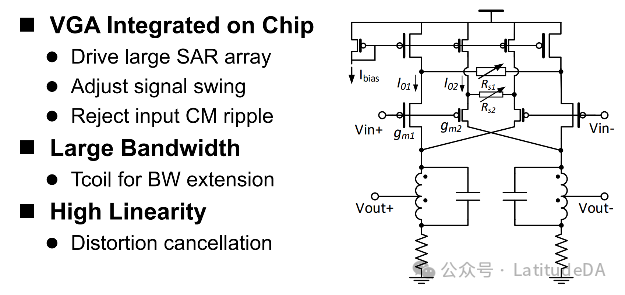

VGA 设计采用了新颖的失真消除技术,如图 3 所示。两个差分对以相反的极性连接,在保持高增益的同时有效地消除了失真。这种消除技术依赖于器件尺寸和电流的比率,因此对工艺、温度和电压变化不敏感。

图 3. 可变增益放大器

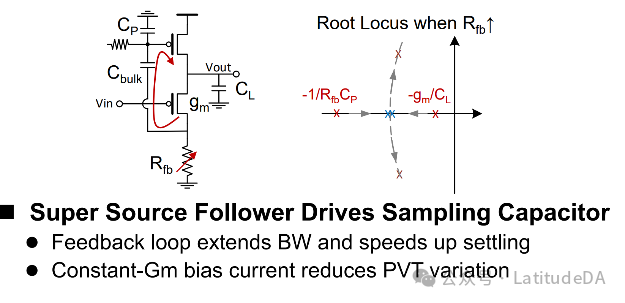

为了解决宽带 T/H 电路中的电容泄漏问题,采用了超级源极跟随器 (SSF) 来驱动采样电容,如图 4 所示。SSF 集成了一个反馈环路,可扩展带宽并加快沉淀时间,同时恒定 gm 偏置电流可减少 PVT 变化。

图 4. T/H 超级源极跟随器

此外,如图 5 所示,通过使用具有电容抵消功能的差分采样开关,电容泄漏效应得到了缓解。该技术可有效消除差分电容泄漏,从而减少符号间干扰 (ISI) 和频率纹波。

图 5. T/H 中的电容泄漏

数模转换器设计

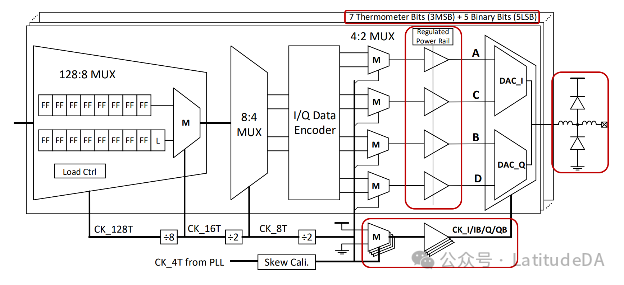

DAC 设计采用四分之一速率时钟和半速率数据结构,如图 6 所示。这种方法具有多种优势,包括由于使用 2T 脉冲的内部信号而降低了功耗,由于只有 50% 的空闲分支而减少了寄生电容,以及对时钟/数据偏移不敏感。

图 6. DAC 结构

为了解决由 I/Q 时钟偏移和占空比失真引起的潜在交织尖峰,采用了片上校准环路。这些环路可确保 I 和 Q 时钟的精确对齐,以及精确的占空比校正,从而最大限度地减少特定频率下的交错脉冲。

DAC 的三个最有效位 (MSB) 采用 7 位温度计编码方案,五个最小有效位 (LSB) 采用二进制编码。这种混合编码方法在面积效率和线性度性能之间取得了平衡。

图 7. DAC 框图

PLL 设计

PLL 设计如图 8 所示,采用电荷泵架构,配备两个低噪声 LC 压控振荡器 (VCO),以覆盖较宽的频率范围。利用差分电荷泵和环路滤波器来增强抗噪能力。

图 8. PLL 框图

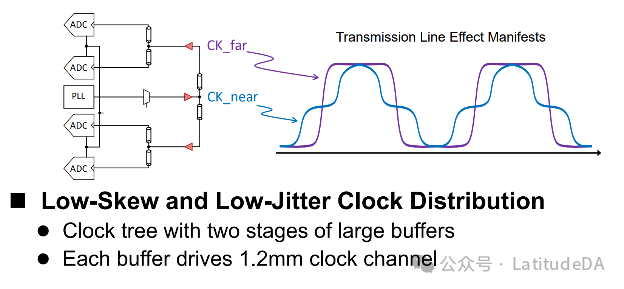

如图 9 所示,通过带有大型缓冲器的两级时钟树实现了高效的全局时钟分配。每个缓冲器驱动一个 1.2 毫米的时钟通道,确保整个芯片的低偏移和低抖动时钟传输。

图 9. 全局时钟分配

测量结果

600Gbps DP-QAM64 相干光收发器前端与 DSP 模块集成在 16nm CMOS 工艺中,表现出令人印象深刻的性能指标。如图 10 所示,模数转换器的带宽超过 40GHz,有效位数 (ENOB) 超过 6 位,最高可达 25GHz。通过失真消除电路,无杂散动态范围 (SFDR) 超过 50.7dB,通过片上校准,交错脉冲被抑制在 -60dB 以下(图 11)。

图 10. ADC ENOB

图 11. ADC 频谱

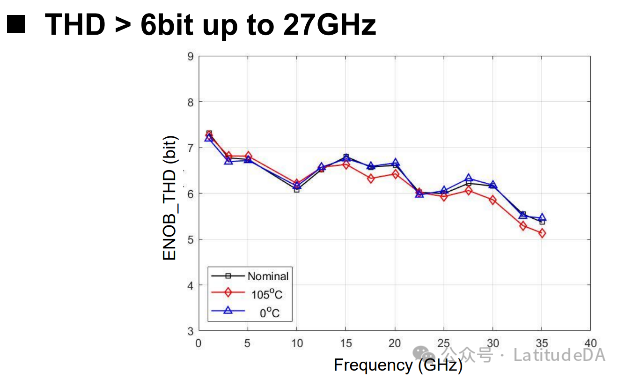

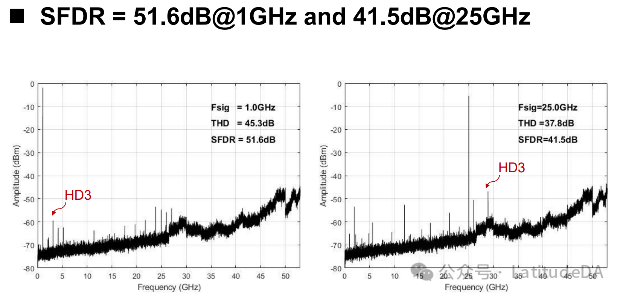

DAC 的带宽超过 35GHz,总谐波失真 (THD) 相当于 ENOB 超过 6 位(最高达 27GHz)(图 12)。SFDR 在 1GHz 时达到 51.6dB,在 25GHz 时达到 41.5dB(图 13)。

图 12. DAC 总谐波失真

图 13. DAC 频谱

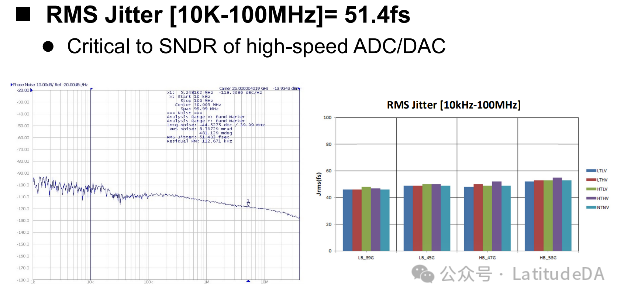

PLL 在 10kHz 至 100MHz 范围内实现了 51.4fs 的均方根 (RMS) 抖动,令人印象深刻,这对于高速 ADC 和 DAC 保持高 SNDR 非常重要(图 14)。

图 14. PLL

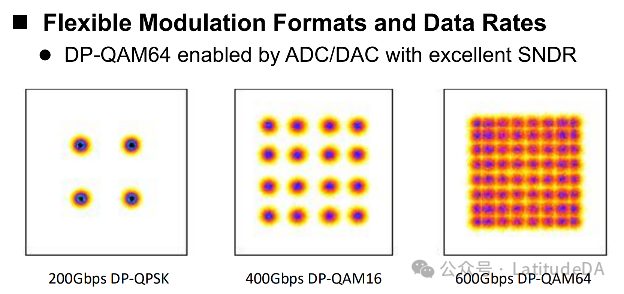

光电环路星座图显示了收发器的灵活性,支持各种调制格式(DP-QPSK、DP-QAM16 和 DP-QAM64)以及 200Gbps 至 600Gbps 的数据速率(图 15)。

图 15. 光电环路星座图

结论

600Gbps DP-QAM64 相干光收发器前端采用 16nm CMOS 工艺实现,代表了高速光通信领域的重大进步。模数转换器、数模转换器和 PLL 模块采用的创新设计技术实现了卓越的性能指标,包括高带宽、线性度和低抖动。

该收发器前端可灵活支持各种调制格式和数据速率,适用于长途、城域和 ZR 应用,目前已投入量产。这一设计的成功实施为未来高速光收发器的发展排除了障碍,从而实现了更高的数据传输速率和更有效的光纤容量利用。

参考文献

[1]G. Li, A. Garg, T. He, U. Singh, J. Zhang, L. Rao, C. Liu, M. Nazari, Y. Liu, H. Zhang, T. Ali, H-G. Rhew, J. Ru, D. Cui, A. Nazemi, B. Zhang, A. Momtaz, J. Cao, "18.1 A 600Gb/s DP-QAM64 Coherent Optical Transceiver Front-End with 4x105GS/s 8b ADC/DAC in 16nm CMOS," in Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) 2024

本文地址:http://www.iccsz.com//Site/CN/News/2024/03/07/20240307012752376953.htm 转载请保留文章出处

关键字:

文章标题:Broadcom基于16nm CMOS工艺的600Gbps DP-QAM64相干光收发器前端设计技术解析

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- · 厦门优迅推出基于CMOS工艺的 10G传输应用低功耗整体解决方案

- · 厦门优迅发布业内首款CMOS低功耗XGSPON OLT DML驱动芯片UX3368

- · 相干光收发器DSP:什么是FEC和PCS,它们为什么重要?

- · CMOS兼容光子集成电路会议在比利时微电子研究中心IMEC召开

- · 上海微系统所实现新型混合集成光量子学芯片

- · CIOE 2021|MaxLinear展示业界首款采用5nm先进工艺的CMOS 800G PAM4 DSP

- · HiLight Semiconductor宣布展示CMOS 25Gbps Combo IC HLC28L0

- · IFOC 2020预告 | 上海光梓工程副总裁陈学峰:硅基CMOS高速光互连IC研发和产业化

- · 解决芯片互连卡脖子问题:CMOS片上光电互连速度突破2Tb/s

- · HiLight宣布CMOS 25Gbps TIA出货量达到100万里程碑

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1