如何制造一个光子集成电路(PIC)芯片?

光子学是未来的赋能技术之一。光是宇宙中最快的信息载体,并且可以在传输这些信息的同时比电信号耗散更少的热量和能量。因此,光子学可以极大地提高通信网络的速度、覆盖范围和灵活性,并应对不断增长的更多数据的需求。而且,它将以较低的能源成本做到这一点,减少互联网的碳排放。同时,快速高效的光子信号在医疗设备、汽车激光雷达、农业和食物诊断等方面的传感和成像应用中具有巨大潜力。

鉴于其重要性,我们想解释一下光子集成电路(PIC),即实现所有这些应用的芯片是如何制造的。

设计一个PIC芯片

设计PIC的过程,是将最初的应用概念转化为可制造的功能性光子学芯片。在2018年OFC会议的一个简短课程中,来自根特大学的Wim Bogaerts总结了典型的PIC设计过程,我们将在本文中介绍这些步骤。

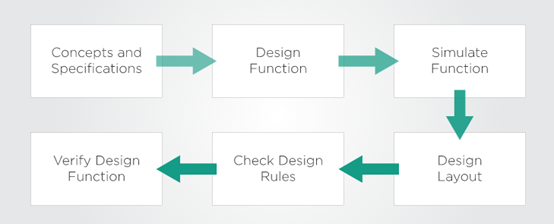

图1:PIC设计流程中的步骤

1、概念和规格。我们首先要定义芯片中的内容。芯片架构师通常会花时间与客户沟通,了解客户希望通过芯片实现什么,以及芯片的所有使用条件和情况。在这些对话之后,芯片应用概念成为一套具体的规格,并传递给芯片设计的团队。这些规格将设定PIC设计的性能指标。

2、设计功能。在确定了规格后,设计团队将开发一个原理电路图,以捕捉PIC的功能。这张图被分成几个功能块:其中一些可能已经存在,另一些可能需要建造。这些模块包括激光器、调制器、检测器和其他能够以某种方式操纵光的部件。

3、设计仿真。制作一个芯片需要花费大量的金钱和时间。面对这样的风险,芯片设计的一个基本要素是准确预测芯片制造后的行为。功能块被放置在一起,并使用各种物理模型和模拟工具对它们的行为进行模拟。设计团队经常使用一些不同的模拟方法来减少制造后的故障风险。

4、设计布局。现在,设计团队必须将功能芯片原理图转化为可制造的适当设计布局。布局由层、元件位置和代表实际制造步骤的几何形状组成。团队使用软件将这些功能转化为要制造的几何图形,对于最棘手的位置和几何形状的决定需要人工干预。

5、检查设计规则。每个芯片制造厂都会有一套自己的制造规则。在这个步骤中,设计团队要验证布局是否符合这些规则。

6、验证设计功能。这是一个最后的检查,以确保布局实际上是按照最初的电路原理图来执行的。布局过程通常会导致新的元件放置和寄生效应,这些都是在最初的电路原理图中没有考虑的。这些测试可能需要设计团队重新审视以前的功能或布局原理图步骤。

PIC芯片制造的众多步骤

制造用于光子学和电子学的半导体芯片是世界上最复杂的过程之一。例如,EFFECT Photonics公司总裁Boudewijn Docter,在他的大学时代就描述了一个总共有243个步骤的芯片制造过程。

埃因霍温科技大学(TU/e)的副教授焦裕庆用几个基本的、简化的步骤来解释制造过程:

1、生长或沉积你的芯片材料

2、在材料上打印一个图案

3、将图案蚀刻在材料上

4、做一些清洁和额外的表面处理

5、回到第1步,根据需要重复

当然,实际过程要复杂得多,需要在上述步骤中循环往复几十次,导致总步骤超过200个。让我们更详细地了解一下这些基本步骤。

图2:半导体制造工艺的基本步骤,在一个制造周期内重复进行。整个晶圆制造过程需要几十个这样的周期。

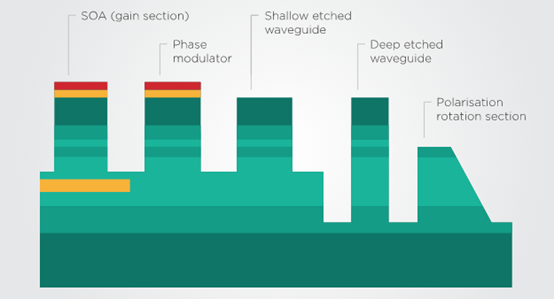

1、层状外延和沉积。不同的芯片器件需要不同的半导体材料层。这些层可以通过一种称为外延的工艺生长在半导体晶圆片上,或通过其他方法沉积。

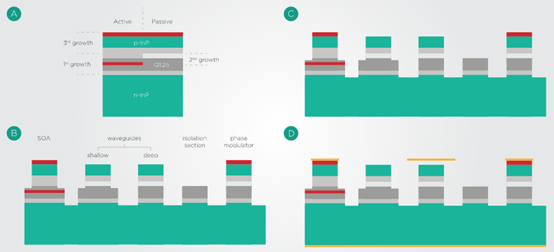

图3:PIC芯片上的器件的简化例子及其所需的不同材料层。资料来源:Smit等人 (2014)

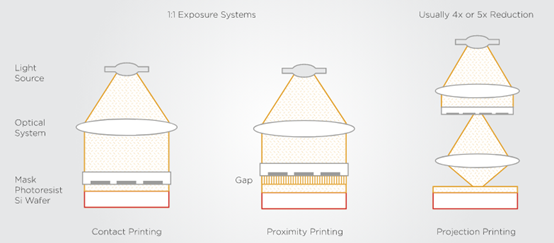

2、光刻技术(即印刷)。有几种光刻方法,但用于大批量芯片制造的是投影光学光刻法。半导体晶片上涂有一种称为光刻胶的光敏聚合物薄膜。同时,设计的布局图案被转移到一种称为掩模的不透明材料上。光学光刻系统将掩膜图案投射到光刻胶上。然后,曝光的光刻胶被显影(像摄影胶片一样)以完成图案印刷。

图4:不同光学光刻方法的比较。接触式和接近式印刷使光罩与样品接触或接近。投影光刻式使光罩保持在较远的地方,最初的成本较高,但它是大批量制造的首选技术。资料来源:滑铁卢大学J: J. Shen, 滑铁卢大学博士论文 (2018)

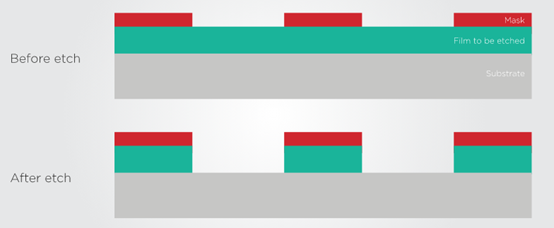

3. 蚀刻:在光阻上 "打印 "出图案后,就需要去除(或蚀刻)部分半导体材料,以便将图案从光阻上转移到晶圆片上。有几种技术可以用来蚀刻材料。

图5:在蚀刻步骤之前和之后,上面有抗蚀剂(红色)的半导体晶圆片的例子。

4. 清洁和表面准备。蚀刻后,一系列的步骤将在下一个周期前清洁和准备表面。

钝化。添加电介质材料层(如二氧化硅)以 "钝化 "芯片,使其更能承受环境的影响。

平面化。使表面平整,为将来的光刻和蚀刻步骤做准备。

金属化。在晶圆上沉积金属部件和薄膜。这可能是为了将来的光刻和蚀刻步骤,或在最后为芯片添加电触点。

图6总结了一个InP光子设备在经过层外延、蚀刻、电介质沉积和平面化以及金属化等步骤后的情况。

图6:半导体晶片结构的横截面:(a)外延生长,(b)蚀刻,(c)钝化和平面化,(d)金属化。

PIC芯片昂贵的测试和封装过程

芯片制造是一个有许多变数的过程,因此需要大量的测试,以确保制造的芯片与最初的设计和仿真一致。一旦这一点得到认证和合格,接下来就是PIC封装的过程。

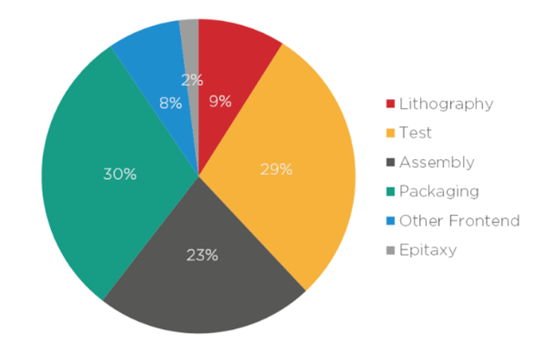

虽然封装和测试的成本只是电子系统成本的一小部分,但光子系统的情况正好相反。埃因霍温技术大学(TU/e)的研究人员估计,对于大多数磷化铟(InP)光子设备,封装和测试的成本可以达到总模块成本的80%左右。有许多研究工作正在进行,以降低这些成本。

图7. 基于InP的 PIC芯片的工艺成本明细,以及占总制造成本的百分比。资料来源:Latkowski等人,2019年

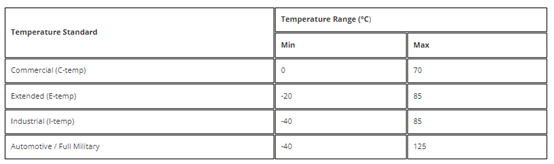

特别是在一个新芯片的第一次流片之后,会有几轮特征提取、验证和修订,以确保芯片的性能符合规格。在这第一轮的特征提取和验证之后,芯片必须为大规模生产做好准备,这需要在几个不同的环境条件下进行一系列的可靠性测试。例如,不同的应用需要对芯片的工作温度进行不同的认证。

表1:比较不同温度硬化标准的温度范围,包括工业、汽车以及全面军事应用

总结

制作光子集成电路的过程是非常漫长和复杂的,本文描述的步骤仅仅是整个过程的简化。它需要全世界不同领域的专家在芯片设计、制造和测试方面的大量知识。EFFECT Photonics公司是由亲自制造这些芯片的人创立的,他们对这一过程有深入的了解,并建立了联系和网络来大规模开发尖端的PIC芯片。

逍遥科技 | 编译自 Effect Photonics

本文地址:http://www.iccsz.com//Site/CN/News/2022/12/09/20221209020012088162.htm 转载请保留文章出处

关键字: PIC 光子集成电路

文章标题:如何制造一个光子集成电路(PIC)芯片?

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- · EXFO完成收购EHVA | PIC测试端到端集成全自动,更高效!

- · 旭创技术研究院推出自研EDA设计软件—PIC Palette

- · IFOC 2022预告 | 日立VLC:PIC development with fabless model

- · EXFO与趋势共舞,领头PIC测试的五大市场预测

- · 首个欧洲绝缘体上铌酸锂PIC平台

- · 光子集成回路Wafer Level Test网络研讨会(演讲视频分享)

- · 日立收购西班牙VLC为子公司 涉足光子集成电路业务

- · Verizon投资NG-PON2光收发器新创公司

- · MEMS技术用于PIC的耦合

- · EXFO强强联手 迎接下一代网络的光子集成电路(PIC)测试挑战

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1