为硅基光电子工艺平台设计高效率、允许高制造容差的双层光栅耦合器

引言

硅基光电子技术利用成熟的 CMOS 制造工艺,已成为实现高度集成光路的一个前景广阔的平台。最广泛采用的平台是绝缘体上硅(SOI)平台,硅核心与二氧化硅包层之间的高折射率对比可实现紧约束光波导。然而,这些纳米级 SOI 波导与标准单模光纤之间存在明显的模式尺寸不匹配,这对光纤到芯片的高效耦合提出了严峻的挑战。

光栅耦合器(GC)因其晶圆尺寸兼容性、宽松的光纤对准公差以及可集成在芯片表面任意位置的能力,已被广泛采用为硅光子学中光纤到芯片耦合的解决方案。虽然在基板中嵌入金属背反射器的 GC 可以实现很高的耦合效率,但其制造可能具有挑战性,而且可能需要非 CMOS 兼容材料。

本文介绍为 220 nm 厚 SOI 平台设计高效、耐制造的双层 GC 的策略。通过引入经过光栅化处理的非晶硅(a-Si)或非晶锗(a-Ge)顶层,耦合效率值可超过 -0.3 dB。

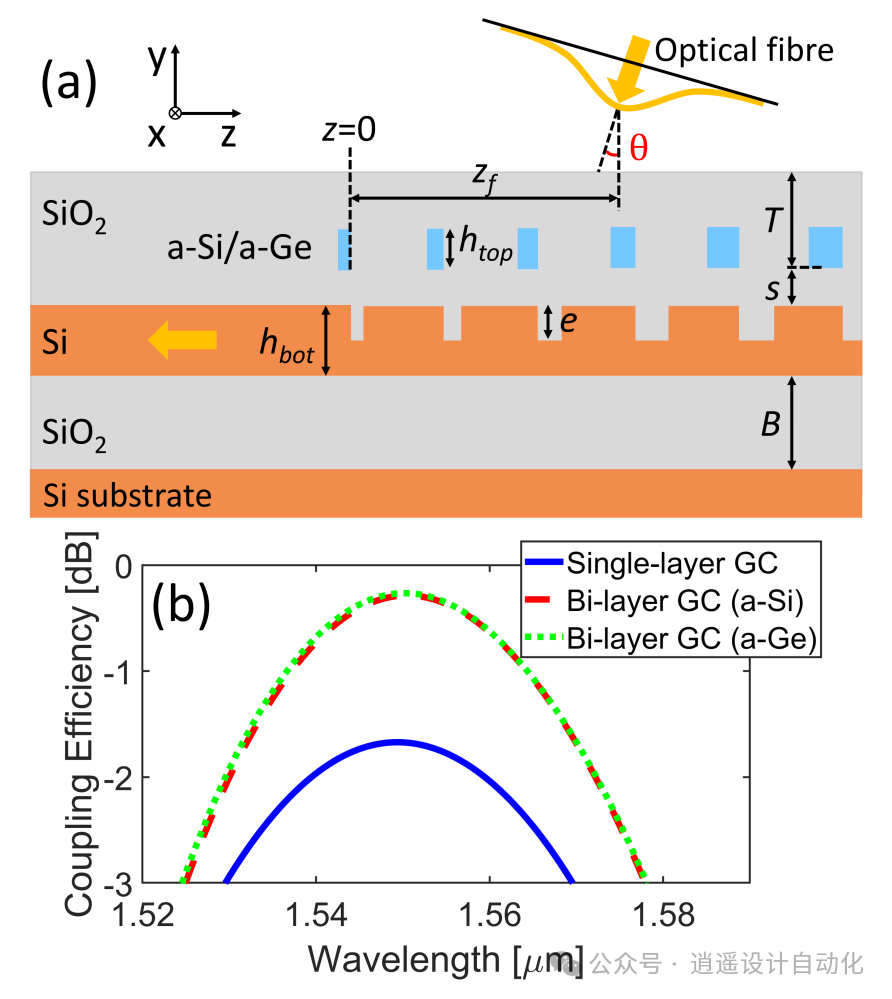

双层光栅耦合器布局如图 1(a)所示,拟议的双层光栅设计由厚度为 220 nm、蚀刻深度为 110 nm 的底层组成,作为光导层。在这层之上,有一个 20 纳米的二氧化硅间隔层,间隔层是一个完全蚀刻的顶层,厚度各不相同(a-Si 或 a-Ge)。

底层和顶层都具有线性光栅化填充因子,光栅化函数的符号相反。此外,每个散射元件的光栅周期都经过重新计算,以满足整个 GC 长度的布拉格条件。采用的最小特征尺寸为 60 纳米,与电子束光刻技术兼容。

图 1:(a)双层光栅耦合器(GC)示意图;(b)单层和双层 GC 跨波长耦合效率(CE)的 3D-FDTD 仿真结果。单层参数:Rbot = 0.0275 µm^-1,zf = 6.2 µm,T = 700 nm。带有 a-Si 覆盖层的双层:htop = 100 nm,Rbot = 0.0291 µm^-1,Rtop = 0.0221 µm^-1,zf = 6.5 µm,T = 540 nm。带有 a-Ge 叠层的双层:htop = 77 nm,Rbot = 0.0322 µm^-1,Rtop = 0.0167 µm^-1,zf = 6.5 µm,T = 550 nm。其他规格包括:hbot = 220 nm,e = 110 nm,B = 2 µm,θ = 14.5°,s = 20 nm,Fin,bot = 0.9,Fin,top = 0.1,GC 宽度 = 14 µm。数值模拟和结果GC 设计过程包括两个步骤。首先,只考虑底层,通过扫描蚀刻深度、底层线性光晕系数和光纤到光栅的距离参数,使用 2D-FDTD 仿真优化其在 1550 nm 波长的耦合效率。随后对优化后的单层 GC 进行 3D-FDTD 仿真,结果如图 1(b)所示,1550 nm 处的峰值耦合效率为-1.67 dB,1dB 带宽为 34.8 nm。

第二步,引入顶层(a-Si 或 a-Ge),并对参数空间进行粒子群优化,包括顶层厚度、光晕系数和光纤到光栅的距离。如图 1(b) 所示,优化后的双层 GC 在 1550 nm 波长处的峰值耦合效率为 -0.29 dB,1dB 带宽为 32.2 nm,而 a-Ge 覆层变体的峰值耦合效率为 -0.27 dB,1dB 带宽为 32.4 nm。

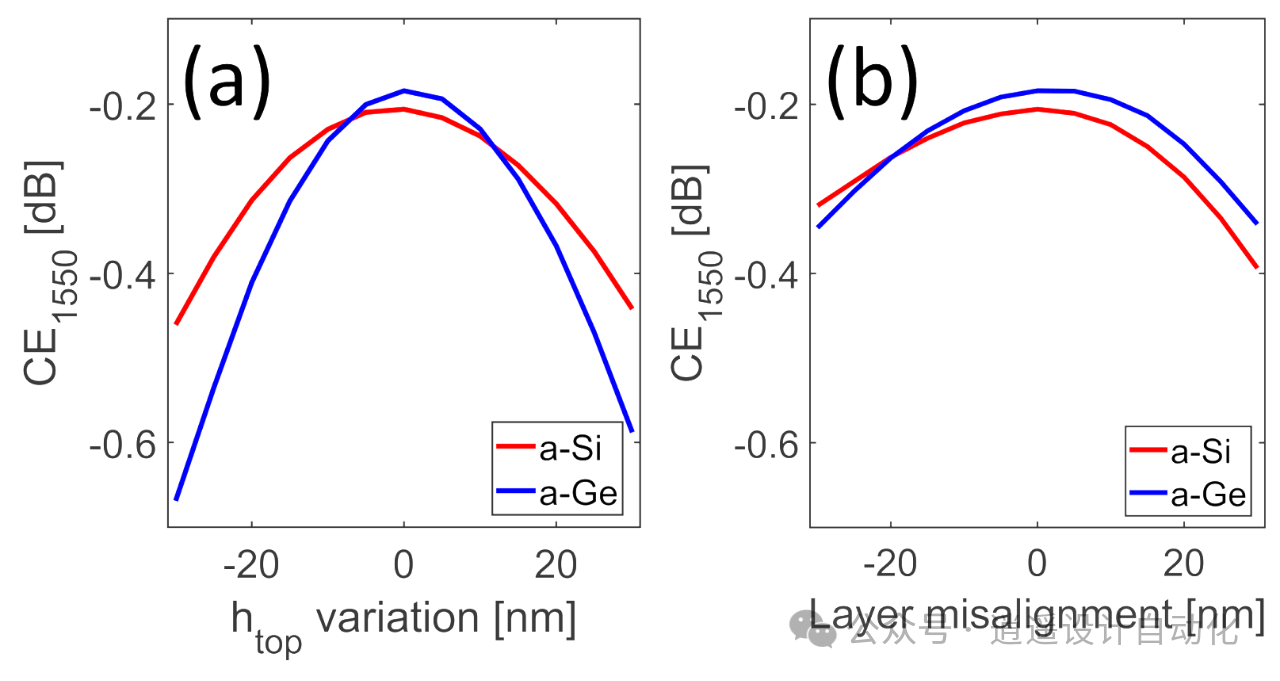

制造容差分析通过研究峰值耦合效率对顶层厚度变化和传播方向层错位的依赖性,评估了双层 GC 对制造误差的敏感性。

如图 2(a) 所示,与 a-Ge 变体相比,a-Si 叠层 GC 由于折射率较低和尺寸较大,对顶层厚度变化的耐受性更好。如图 2(b)所示,两种设计对层错位的制造容差都比较宽松。

图 2. GC 对关键制造参数的敏感性:CE1550 对 (a) 顶部厚度 htop 变化和 (b) 层错位的依赖性。

结论

本文介绍设计高效双层 GC 的策略,其基础是在 220 nm 厚的 SOI 平台上使用 a-Si 或 a-Ge 叠层。数值模拟显示,这两种方法在电信 C 波段的峰值耦合效率值均大于 -0.3dB,1dB 带宽均大于 32 nm。就叠层厚度而言,非晶硅叠层 GC 具有更好的制造容差,而两种设计对层错位的制造容差都比较宽松。

所提出的双层 GC 设计为硅基光电子集成电路中高效、稳健的光纤到芯片耦合提供解决方案,使从电信到传感和计算等各种应用中的高性能光互连成为可能。

本文地址:http://www.iccsz.com//Site/CN/News/2024/07/07/20240707151145163516.htm 转载请保留文章出处

关键字:

文章标题:为硅基光电子工艺平台设计高效率、允许高制造容差的双层光栅耦合器

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- · 通用单元硅基光电子集成电路的全局优化

- · Quintessent募集1150万美元种子基金,打造面向未来的高速光互连

- · 硅基光电子技术:台积电副总经理张晓强博士在IEEE年度盛会ISSCC上的见解

- · 以色列的重点新技术领域:硅基光电子、超构表面材料、黑兵蝇养殖

- · NIST和AIM Photonics合作开发高频硅基光电子芯片

- · 北京大学研究出由集成微腔光梳驱动的硅光片上集成系统

- · 「创言」合创资本王先根:21世纪硅基光电子的投资机遇与挑战

- · 国家信息光电子创新中心牵头完成的《硅基光电子集成技术前沿报告》在CICC 2020成功发布

- · 硅基光电计算

- · 中外高手“宁”聚芯动力 论剑硅基光电子创新发展

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1