先进封测系列|破解光子芯片(PIC)“测前难”,晶圆级测试是关键!

ICC讯 在AI大模型与算力基础设施快速演进的驱动下,智算中心正加速迈向“以光为核心”的互联新时代。光子集成电路(PIC)凭借高带宽、低功耗、小尺寸等优势,成为支撑高性能计算的关键技术。然而,制约PIC规模化应用的瓶颈不在设计,而在制造与测试环节。传统模块级测试已难以满足硅光芯片对一致性和良率的要求,推动测试向封装乃至晶圆阶段前移,成为提升产能与加速应用落地的关键路径。

本文将深入解析PIC互联的发展趋势与测试挑战,并探讨EXFO OPAL自动化探针平台在晶圆级边缘耦合测试中的的应用能力,助力光子集成芯片实现规模化、高效落地。

AI驱动下的互联瓶颈与测试挑战

— 行业背景 —

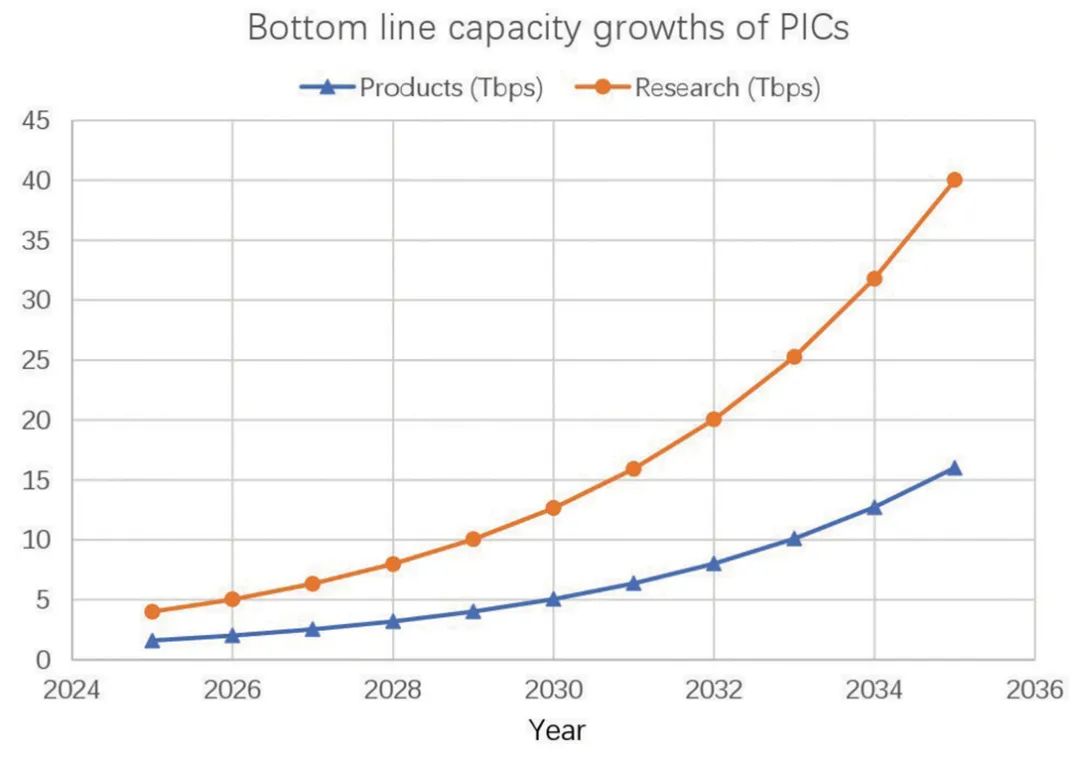

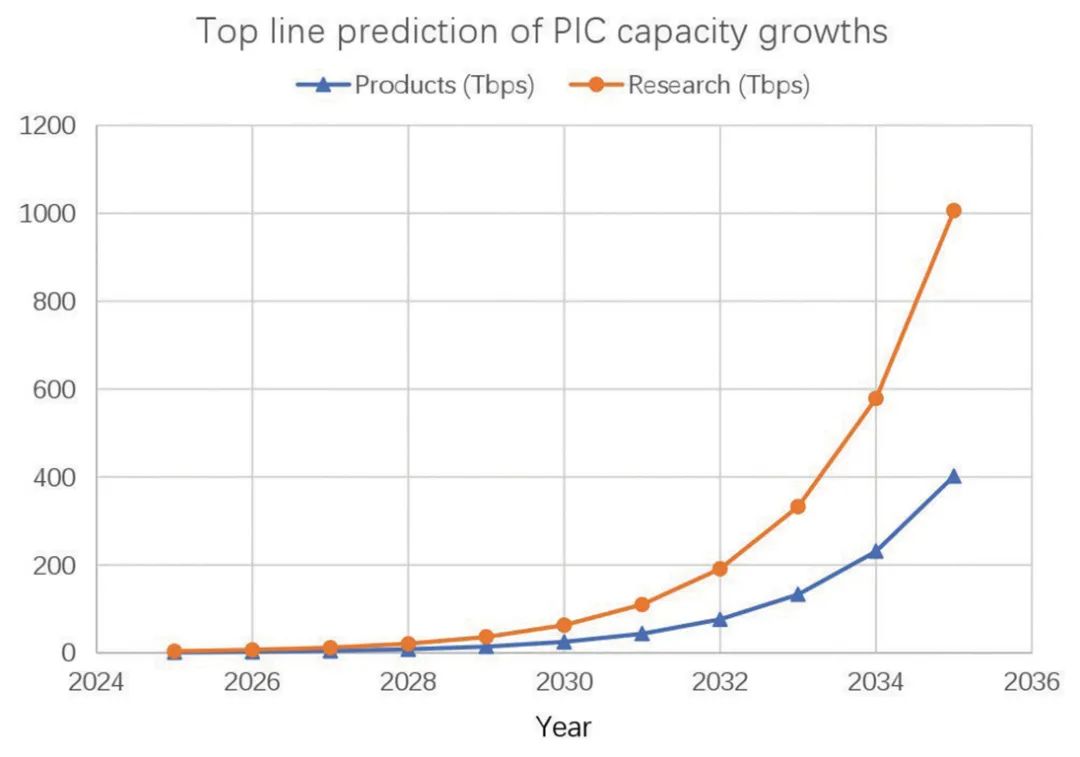

近年来,AI大模型参数规模呈指数增长,GPU算力持续攀升,而网络带宽提升仅为1.4倍,形成明显“剪刀差”,网络系统正成为限制智算中心效率释放的核心瓶颈。光互联,尤其是基于PIC的高速并行架构,被视为是打破瓶颈的关键路径。然而,PIC的大规模落地面临严峻挑战,尤其在测试环节。随着芯片容量向百Tb/s甚至Pb/s演进,集成规模与通道数量激增,带来三大难题:

制造复杂度高:单颗芯片集成上千个光学器件,面积大、通道多、功能耦合复杂;

测试难度剧增:传统模块级测试阶段滞后,易造成材料与工艺浪费,且难以实现闭环控制;

良率风险上升:缺乏晶圆级系统功能验证,导致缺陷芯片在后段工艺中暴露,拖慢量产节奏。

据统计,TAP(测试、组装与封装)成本已占据PIC芯片制造成本的80%以上,远高于传统电芯片。

从参数验证到系统功能全保障— 测试体系 —为确保PIC芯片在高复杂度应用场景下的性能稳定与制造良率,光学测试贯穿从设计验证到模块交付的全流程。根据测试阶段和目的不同,可分为三大阶段与两类方法。

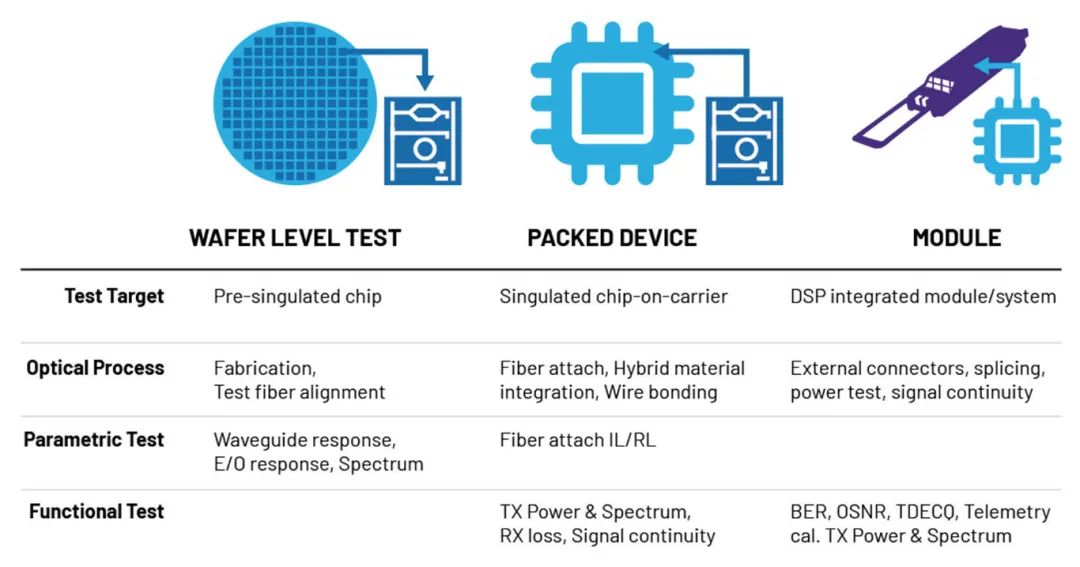

三大测试阶段:

晶圆级测试:在芯片切割封装前进行,聚焦插入损耗(IL)、偏振相关损耗(PDL)等基础光学参数,及早筛除缺陷芯片,提升良率、控制成本;

封装级测试:在芯片封装后进行,验证耦合效率、封装应力等因素对性能的影响,是连接前端制造与后端系统集成的关键环节;

模块级测试:面向完整模块(如OSFP/QSFP),验证误码率(BER)、眼图、TDECQ、发射功率等系统级指标,是出厂前的质量终检。

两类测试方法:

参数测试:聚焦器件结构与材料特性,如带宽、损耗、响应速度等,常用于设计验证与工艺优化;

功能测试:模拟真实应用环境,评估芯片在特定波长、速率、调制格式下的整体性能,如误码率、信噪比等,随着集成度提高,测试复杂性显著增加。

科学划分测试阶段、匹配适当测试方法,已成为提升PIC制造效率与一致性的关键策略。尤其是在量产阶段,晶圆级功能测试正成为突破测试瓶颈、加速产业化的关键抓手。

功能测试前移,晶圆级验证成焦点

— 技术趋势 —

随着PIC芯片集成度、复杂性和应用场景不断提升,行业已形成共识:系统级功能测试必须从传统的模块阶段前移至封装乃至晶圆阶段。这一趋势不仅是技术演进的结果,更是保障良率、控制成本和实现高质量交付的必由之路。

为何测试必须前移?

将测试前置,可在制造早期识别功能缺陷,避免不良芯片流入高成本工序,从根本上降低返工与浪费。具体优势包括:

成本控制:早期筛除不良品,减少封装与组装阶段的高额损失;

效率提升:精简模块级测试流程,加快产品交付节奏;

质量保障:更早发现系统级偏差,提升芯片一致性与可靠性;

工艺闭环:测试数据反馈制造环节,助力设计与工艺持续优化。

前移测试的技术挑战:

尽管趋势明确,实现晶圆级功能验证仍面临不小挑战,主要包括:

高精度耦合难:需实现多通道、大阵列、低插损的边缘耦合,对对准精度和重复性提出更好要求;

指标测量复杂:覆盖BER、TDECQ、Q-factor、IL、RL、PDL等关键系统级指标的精准测量;

平台兼容性要高:测试平台需适配多种材料(Si、InP、LiNbO₃)与封装形态(CPO、MCM等);

自动化与智能化需求高:需支持并行通道控制、实时数据采集与联动,实现“边测边调”、“在线调优”。

在通道密度与传输速率持续提升的背景下,晶圆级功能测试不仅是控制成本的利器,更成为保障良率与大规模交付的核心能力。面向未来,业界亟需构建支持多阶段、多通道、多耦合形态的柔性自动化测试平台,推动PIC测试体系全面升级。

EXFO构建PIC智能测试平台体系

— 解决方案 —

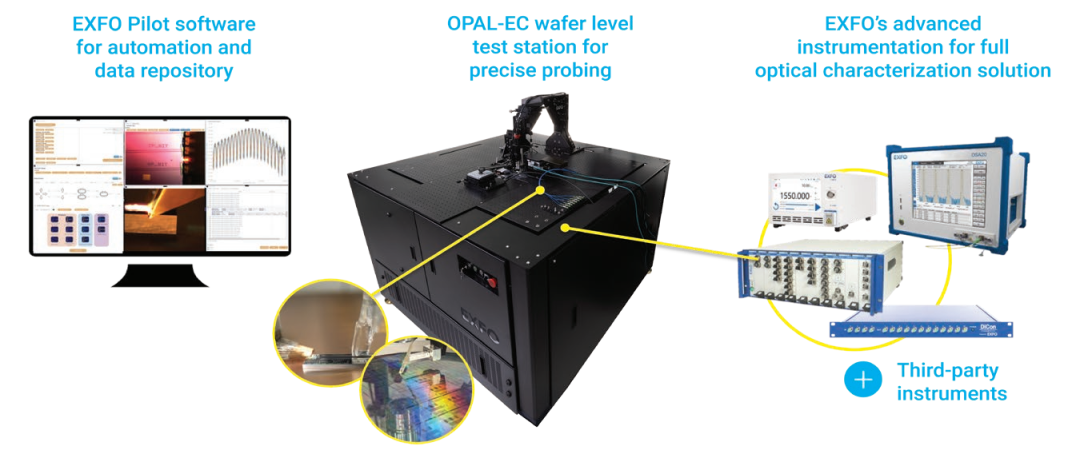

为满足功能测试前移、晶圆级验证及量产需求,EXFO推出OPAL系列自动化探针平台,构建覆盖从科研验证到批量交付的端到端测试体系。平台具备高度自动化、模块化与柔性扩展能力,支持从单裸片到300mm晶圆的多封装形态测试和多光学耦合方式,打通晶圆—封装—模块的测试闭环,是实现光子芯片高质量交付的关键工具。

1. 多封装形态支持:OPAL系列探针台

OPAL-EC|晶圆级边缘耦合测试旗舰平台

专为晶圆级边缘耦合自动化测试打造。平台支持最大300mm晶圆、105°旋转台和多通道并行耦合,集成纳米级对准模块、上下双摄像头系统与自动对焦导航功能,具备0.5nm对准分辨率和3nm晶圆定位精度,显著提升耦合效率与测试一致性。

典型应用: 硅光调制器、MRR等晶圆级器件批量测试;AI、通信、传感场景的大规模PIC筛选与验证;多端口、高密度晶圆级边缘耦合的快速验证。、

OPAL-MD|连接研发与量产的多芯片测试平台

适用于多裸片或复杂封装(如MCM、CPO)测试,适配中试与小批量量产旋球。平台支持多芯片并行测试,内嵌PILOT自动化控制软件,涵盖芯片导向、校准、执行与数据分析的全流程,具备灵活配置能力,满足复杂封装结构的批量验证需求。

典型应用:MPW流片项目与多芯片集成模块评估;高速CPO与复杂封装功能测试;电信模块、自动驾驶领域等中试验证。

OPAL-SD|科研与小批量验证的灵活平台

面向高校、科研机构与初创团队的入门级半自动探针平台,适用于单芯片、小批量的光学/电气功能快速验证。平台支持手动与半自动操作,配备模块化光学/电探针,具备精准对准与灵活切换能力。内嵌PILOT测试软件,支持基础自动控制、数据采集与分析,是科研验证与技术孵化的理想选择。

典型应用:PIC芯片早期设计评估与功能验证;教学实验、技术孵化、工艺初筛;学术研究、初创公司小批量开发测试。

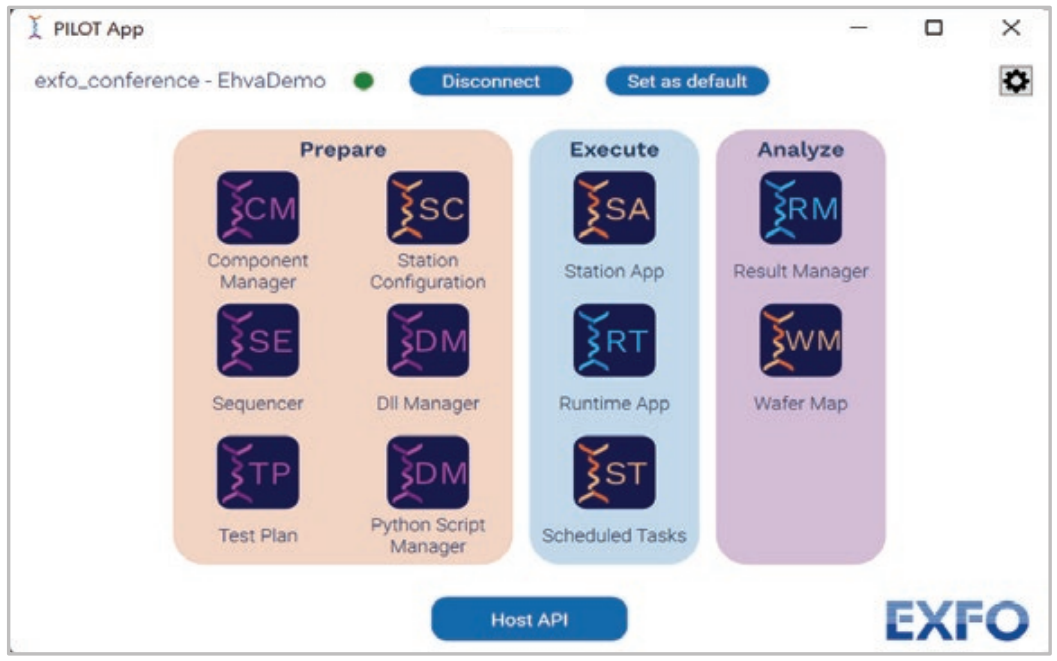

2.PILOT软件平台:数据驱动的智能测试中枢

PILOT是EXFO专为OPAL探针平台打造的核心控制软件,贯穿测试配置、设备控制、流程执行、数据分析与报告生成,构建起可自动化、可追溯、可扩展的PIC芯片测试闭环。其模块化架构与强互操作性,支持从单Die到晶圆、从研发到产线的全流程测试需求。其核心能力包括:

流程自动化与设备联控:自动读取CAD 图纸、识别Die布局,联动激光器、误码仪、功率计等设备,实现对准、校准、采集全流程控制。

灵活脚本与并发调度:内置Sequencer模块,支持Python/Excel脚本、多线程并行与测试序列调度,适配多通道场景。

结构化数据管理:内置云端/本地数据库,实现测试计划、组件定义、配置参数与测试结果的集中管理,支持多站点协同与可追溯数据分析

AI 驱动跳测优化:PILOT原生兼容AI工具,可训练并部署模型,识别缺陷模式、预测结果,智能跳过冗余测试,显著提升良率与测试效率。

强互操作性生态:可与Excel、MATLAB、Power BI等工具无缝集成,助力用户高效完成数据分析与报告生成。

PILOT平台真正实现了从“静态验证”向“动态调参”、从“单点测试”向“流程协同”的跃迁,是支撑晶圆级PIC芯片自动化测试走向产业化的核心软件枢纽。

3. CTP10测试平台:高精度功能测试引擎

CTP10是EXFO推出的高性能光子器件测试平台,专为微环谐振器、MZI、滤波器、VOA等无源和有源器件的参数验证设计,具备高精度、广覆盖、强扩展等优势,是PIC功能验证的关键测试引擎之一。核心优势包括:

亚皮米级分辨率:支持20fm级光谱扫描,满足高Q值微环器件的精细频域响应测试;

超宽波长覆盖:1240–1680nm全波段覆盖,适用于电信、数据通信与生物传感等多应用场景;

超高动态范围:>70dB插入损耗动态范围,单次扫描完成IL、PDL、光谱响应等多项参数测量;

多通道阵列支持:支持100+通道并行测量,适配AWG与光开关等高密度器件阵列测试需求;

激光器稳定与溯源校准:内置DFB激光器与功率校准模块,实现输出稳定性与全流程数据可溯源。CTP10采用模块化设计,支持SCPI命令行与GUI图形界面双重控制,并与PILOT软件无缝集成,适用于研发、中试及量产环境,是当前PIC测试中兼具精度、速度与扩展性兼具的标杆方案。

随着PIC芯片集成度和复杂度的持续攀升,测试正从传统的“事后验证”走向“前置嵌入”。EXFO以OPAL探针台、CTP10测量平台与PILOT自动化软件,构建起覆盖晶圆到系统的智能测试体系,实现高精度耦合、多通道并行、AI辅助分析与数据驱动决策,加速PIC芯片从实验室走向规模应用。在测试战略前移的大趋势下,测试正从辅助工具,演进为驱动光子制造流程优化与产业协同的中枢力量。

本文地址:http://www.iccsz.com//Site/CN/News/2025/07/15/20250715094637192507.htm 转载请保留文章出处

关键字:

文章标题:先进封测系列|破解光子芯片(PIC)“测前难”,晶圆级测试是关键!

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1