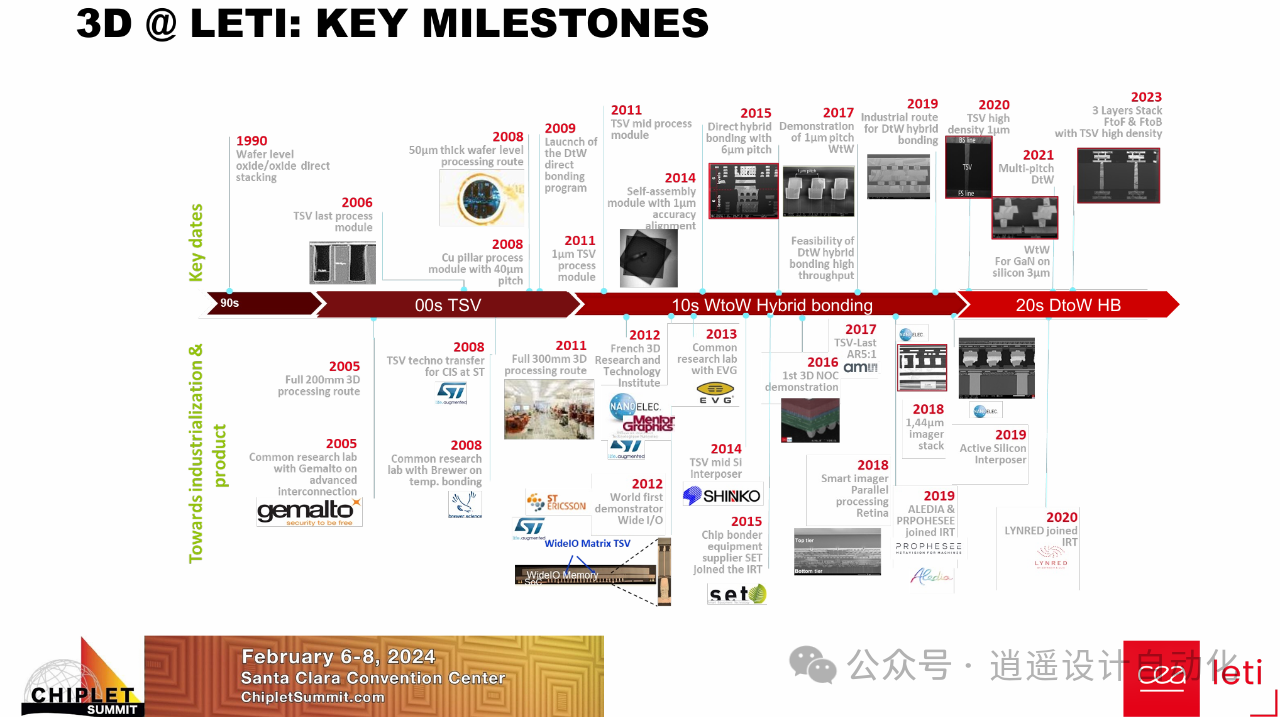

CEA-Leti用于Chiplet的异构集成晶圆级技术

简介

随着电子器件对更高性能和更多功能的需求日益增长,传统半导体的扩展正受到物理限制。通过先进封装实现的chiplet集成正在成为继续推动系统级改进的方法,允许将针对不同功能进行优化的不同chip("chiplet")组合到单个封装中。

本文将介绍为实现高密度chiplet集成而正在开发的关键晶圆级技术,重点介绍 CEA-Leti 正在开展的工作。我们将探讨三维集成背后的动机,概述相关工艺,并探索一些前沿应用。

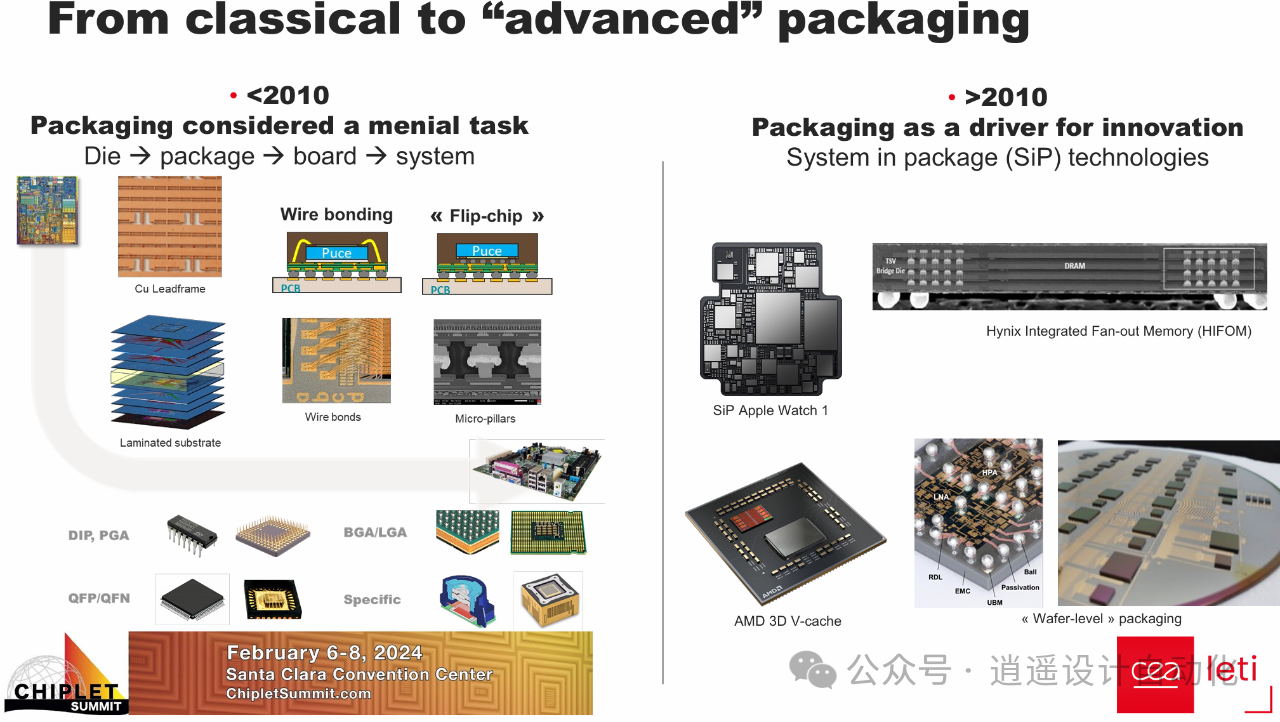

从传统封装到先进封装

一直以来,封装被视为封装单片集成电路芯片的一个相对简单的步骤。但在过去的十多年中,封装技术本身已成为创新的驱动力,促成了全新的系统级封装(SiP)架构,如首款 Apple Watch 和 AMD 的 3D V-cache。

三维电路的形态

三维集成电路由多个垂直堆叠和互连的薄半导体层组成。关键要素包括:

厚度在 50 微米以下的薄堆叠层

层内垂直互连,如连接各层正反面的硅通孔 (TSV)

层与层之间的垂直互连,提供高密度三维集成

使用再分布层 (RDL) 的层内二维互连

晶圆到晶圆键合技术

晶圆到晶圆键合是堆叠减薄半导体层的关键工艺之一。这需要将芯片减薄至 50 微米或更薄的技术,将它们暂时粘合到机械载体芯片上,然后在加工后进行剥离。

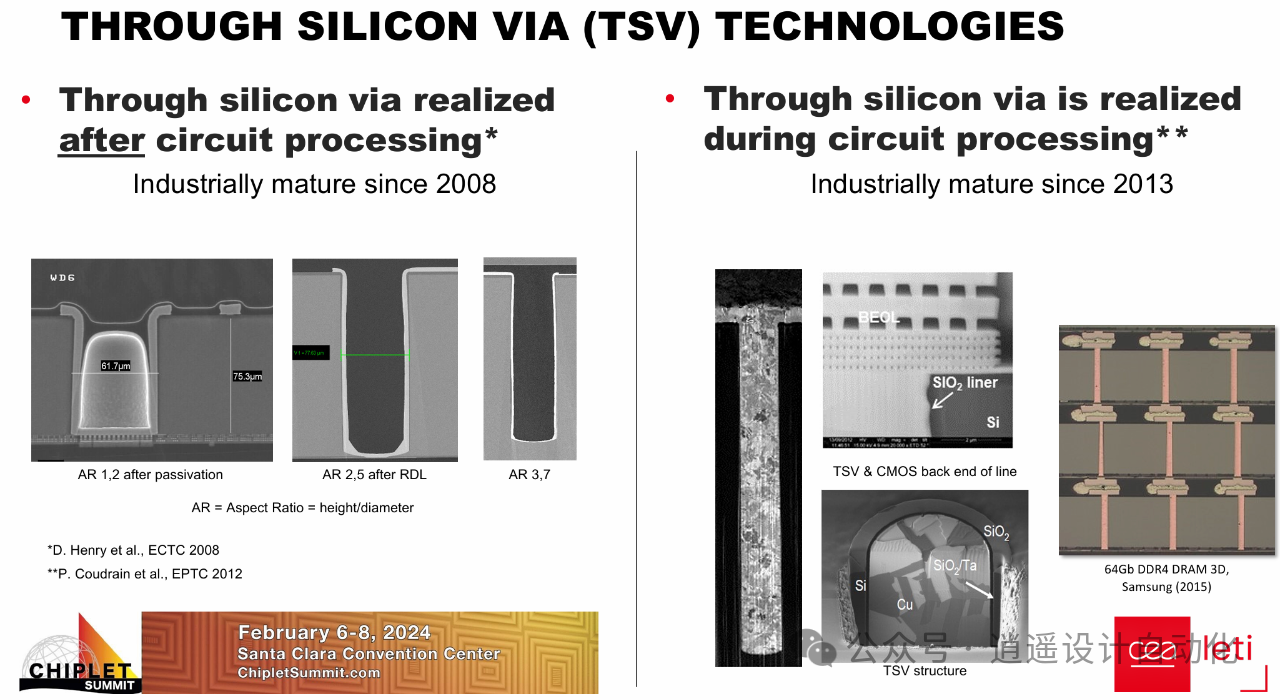

硅通孔 (TSV) 技术

TSV 是穿过半导体芯片的垂直互连器件,用于连接堆叠层,可以在标准 CMOS 加工流程之前或期间制造。可实现的纵横比(深度/宽度)是一项关键指标。CEA-Leti 已经展示了高达 3.7 的高纵横比 TSV,并正在进一步扩展,以实现更高的密度。

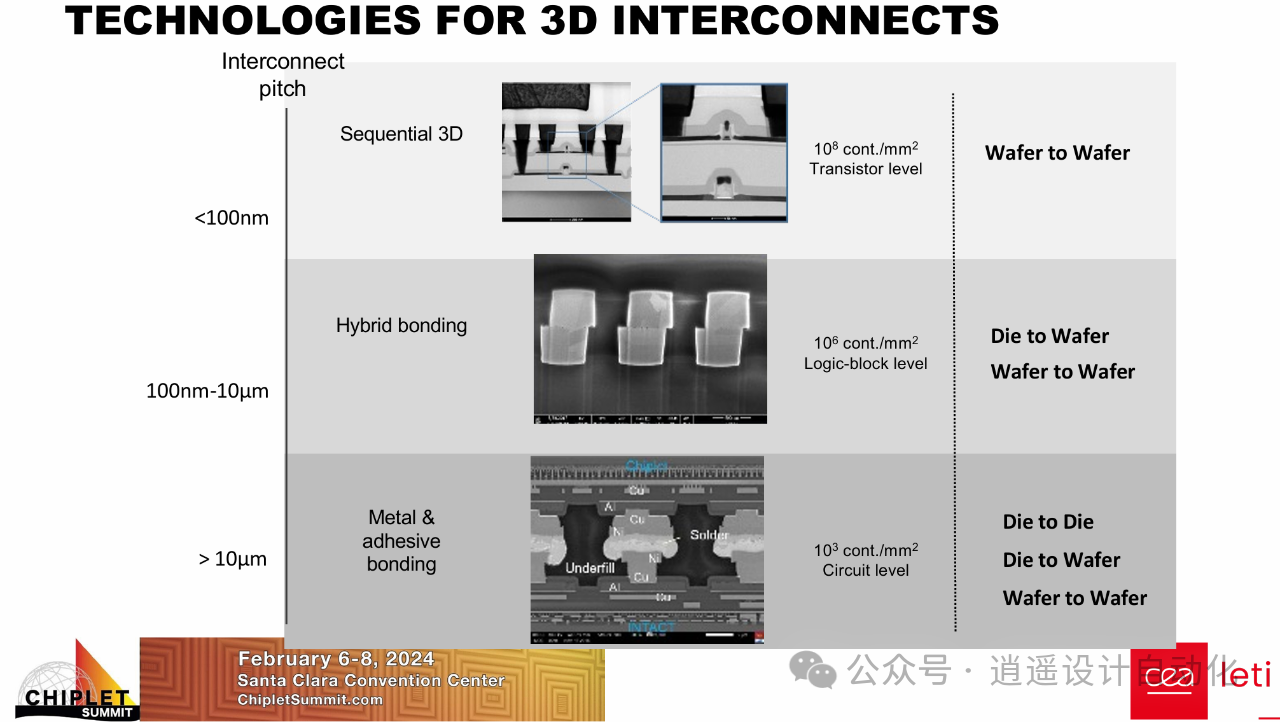

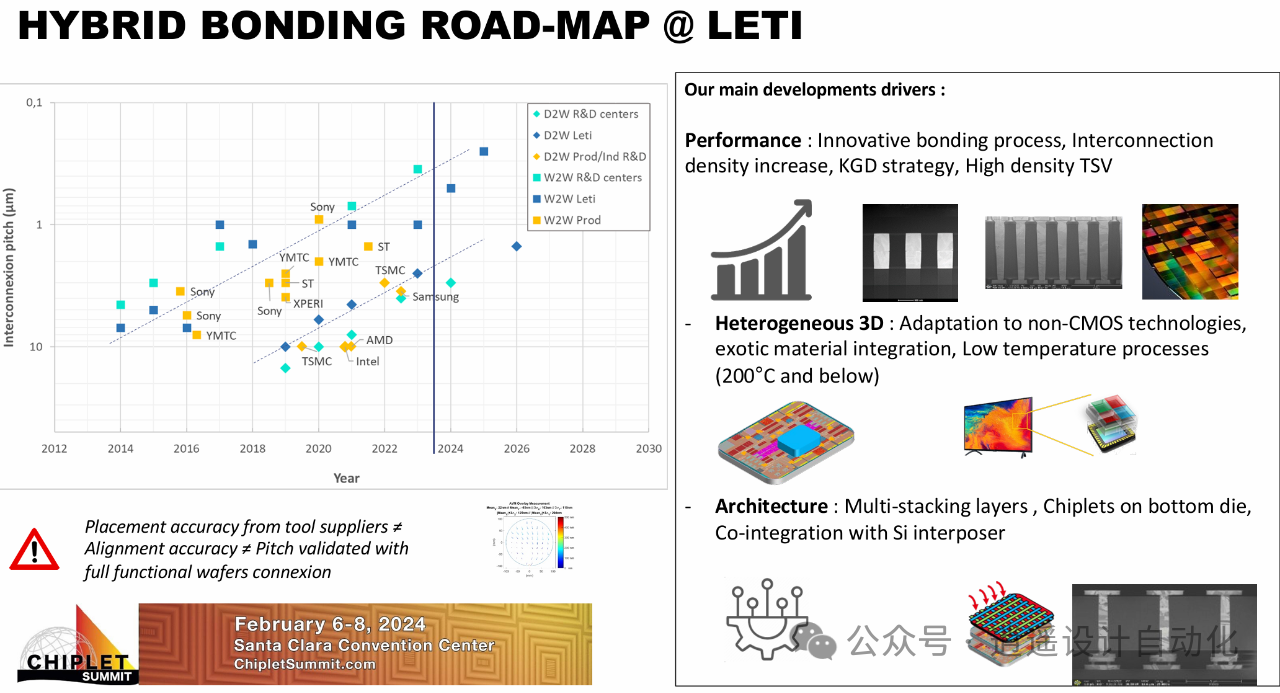

三维互连技术

垂直互联密度是关键因素,不同的组装技术具有从 10^3 到 10^8 互联/mm^2的巨大范围。在一个极端,使用热压焊的焊料微凸块技术可以实现低至 20 微米左右的间距。在另一端,直接混合键合等新兴技术可实现小于 100 纳米的互连间距。

直接混合键合

直接混合键合是实现最高互连密度的关键技术。利用原子平面半导体和金属表面之间的范德华力和共价键合力,在不添加材料的情况下将表面粘合在一起。

工艺流程包括专门的 CMP,以达到所需的 0.5nm RMS 以下的表面粗糙度,然后进行室温键合和退火以加强键合。氧化物和铜-铜键合界面均可使用。

CEA-Leti 和其他公司都在积极开发这一工艺,同时保持合适的设计规则手册和较窄的工艺窗口。

异质键合应用

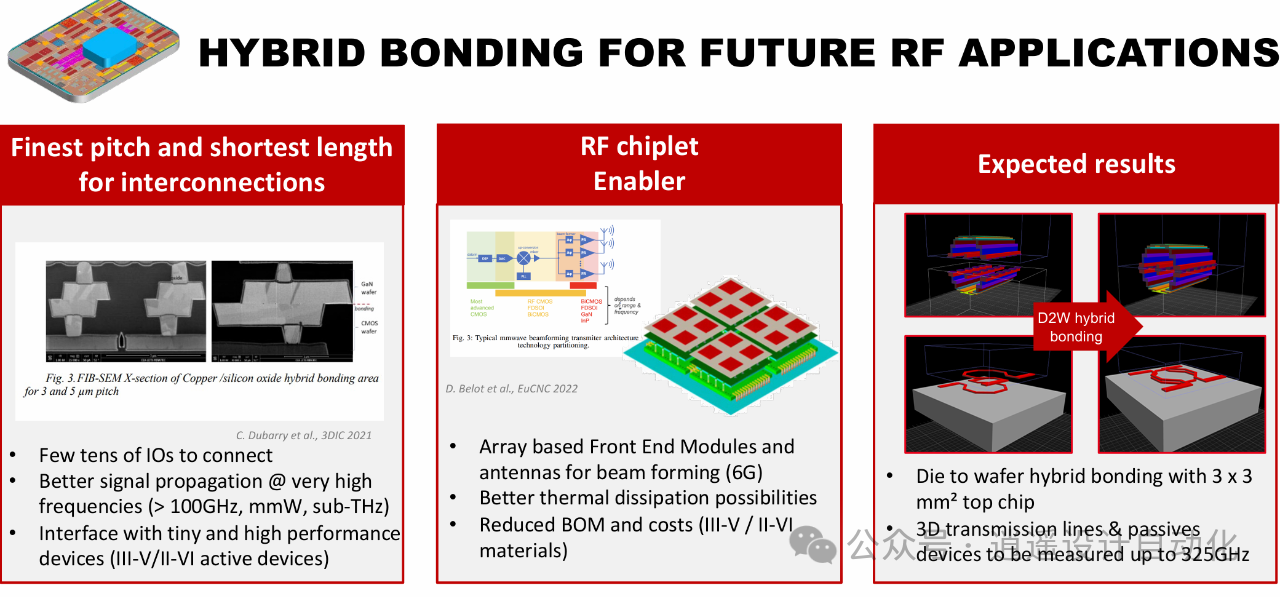

除了传统的逻辑对逻辑三维堆叠外,直接混合键合还能实现不同材料和器件的异质集成。CEA-Leti 正在研究的应用实例包括:

将μLED 阵列与用于微型 LED 显示器的 CMOS 驱动器结合在一起

将 III-V 器件与硅结合,用于射频/毫米波前端和相控阵天线

将针对不同功能(如 CPU、GPU、内存)优化的chiplet堆叠到有源硅interposer上’

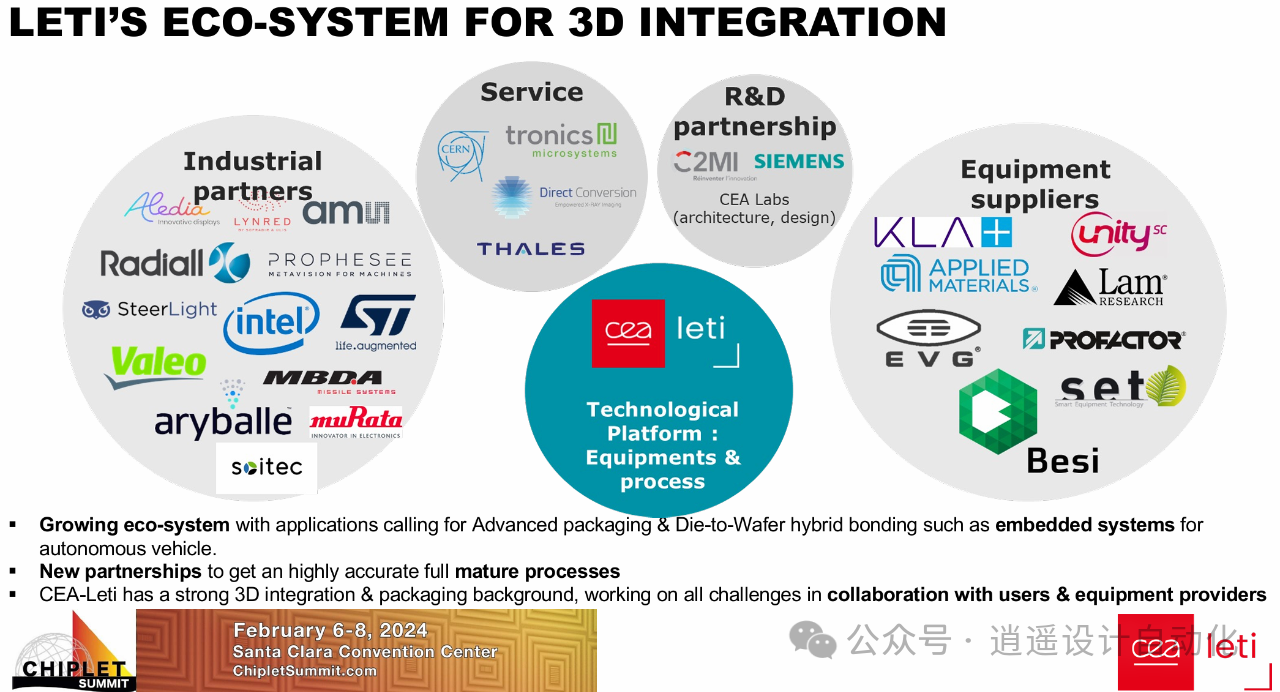

CEA-Leti生态系统

CEA-Leti 已经在工业界、学术界和设备供应商之间建立了广泛的合作伙伴生态系统,以继续推进三维集成技术的发展。他们的背景涵盖了所有挑战,从薄晶圆处理、键合工艺开发到系统级架构设计。

随着自动驾驶汽车、人工智能加速器和 6G 通信等应用对更高计算性能和硬件集成度的需求日益增长,先进封装和Die到晶圆混合键合将继续成为关键的使能能力。

结论

通过先进的晶圆级封装实现异质chiplet集成是颠覆性的方法,可使半导体规模持续扩大,超越仅靠传统单片工艺改进所能实现的规模。本文所涉及的技术,如晶圆到晶圆键合、高纵横比 TSV、微凸块组装,特别是直接混合键合,通过将以前独立的半导体元件组合成紧密集成的三维封装,正在开启新的系统架构。

虽然仍然存在巨大的挑战,但以模块化、可互换的方式灵活混合不同的工艺节点、材料和优化的功能块,有望带来显著的系统级优势。随着主要行业参与者和 CEA-Leti 等研究机构推动这些异构集成能力的发展,我们可以预见,未来几年将有越来越多基于chiplet的创新产品投放市场。

参考文献

[1]S. Joly, "Heterogeneous Wafer Level Technologies for Chiplet Integration," presented at the B-201 Conference, Feb. 2024. Available: /mnt/data/20240208_B-201_Joly.pdf.

本文地址:http://www.iccsz.com//Site/CN/News/2024/06/11/20240611035054133958.htm 转载请保留文章出处

关键字:

文章标题:CEA-Leti用于Chiplet的异构集成晶圆级技术

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1