Marvell基于5nm工艺用于800Gbps相干光通信的发射器解说

简介

云计算和人工智能推动了数据流量的指数级增长,从而刺激了对更高速相干光通信链路的需求。下一代相干光通信的目标是每波长 800Gb/s,即波特率超过 139GBd,发射器数模转换器(DAC)的采样频率介于 60-160GS/s 之间。要在满足大带宽(>60GHz)、低随机抖动(<100fs)和多通道同步等严格要求的同时实现如此高速度,极具挑战性。本教程讨论Marvell在ISSCC2024发表的 8 位 160GS/s、57GHz 带宽的交错时间 DAC 和基于驱动器的发射器,采用了新颖的校准技术来克服这些设计障碍[1]。

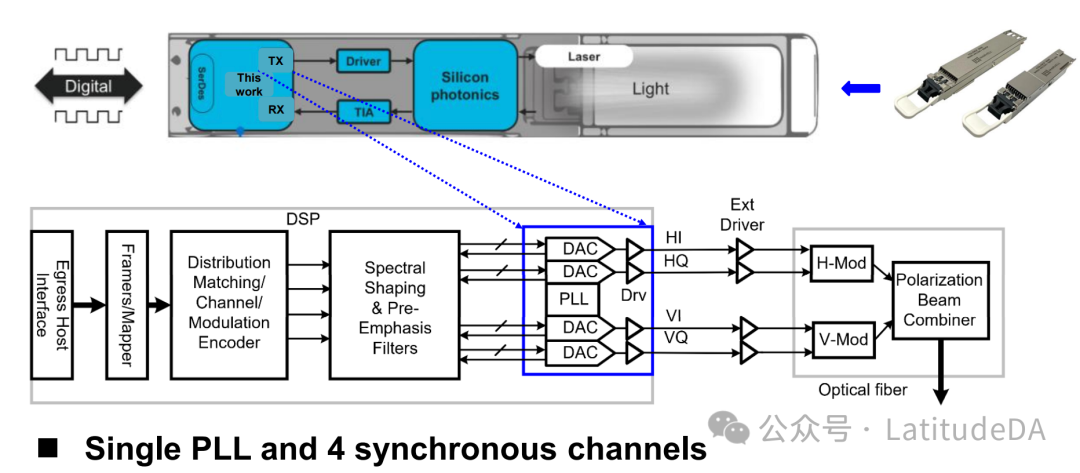

相干光收发器架构相干光收发器架构由发射器(TX)和接收器(RX)组成,如图 1 所示。发送器采用四个同步信道来产生两个极化的同相和正交分量。每个通道都包含一个时间交错 DAC 和串行器,以实现所需的高采样率。

图 1. 相干光学发射机

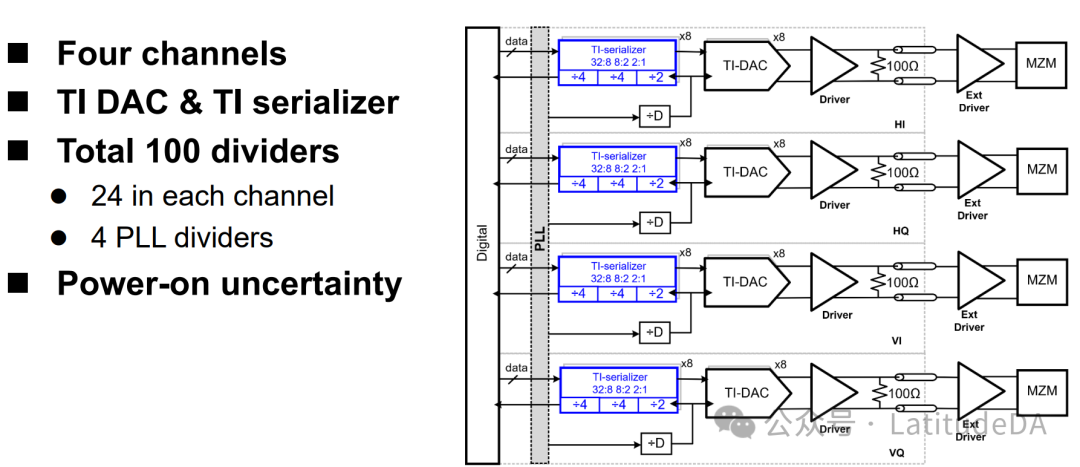

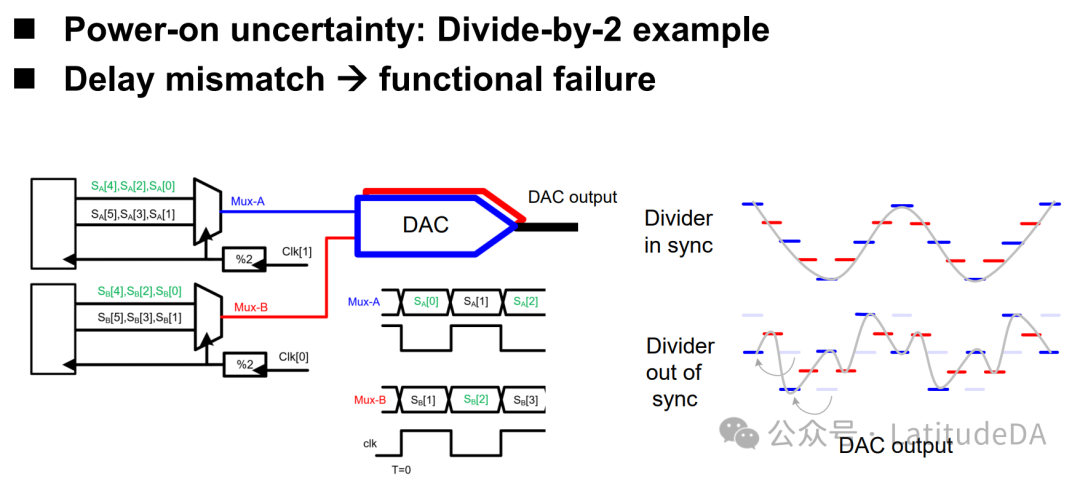

设计挑战- 波特率 > 139GBd:DAC 必须以 60-160GS/s 的最低采样频率运行,以支持超过 139GBd 的波特率。- 大带宽:发射机输出的带宽必须大于 60GHz,以尽量减少符号间干扰。- 低随机抖动:随机抖动应小于 100fs rms,以确保接收器能可靠地恢复数据。 - 通道同步:四个通道必须精确同步,以避免因时间交错架构中 100 多个分频器之间的延迟不匹配而导致功能故障。 通道和时交串行器同步如图 4 所示,时间交错串行器中各分频器之间的上电延迟不确定性会导致 DAC 片和串行器输出之间的不对齐,从而造成功能故障。为了解决这个问题,使用了一条具有自动相关性的模拟环回路径来测量延迟失配,然后通过调整每个通道的延迟线来均衡数字域(图 6)。这种同步技术使所有通道和串行器片段都能正常工作。

图 2. 相干发射机的设计挑战

图 3. 通道和 TI 串行器同步

图 4. 通道与 TI 串行器同步

图 5. 通道和 TI 串行器同步

图 6.提出的同步方法

交错时间 DAC 架构和校准DAC 内核采用具有 8 个片段的时间交错架构,以实现 160GS/s 的采样率(图 7)。每个片由 2 位温度计编码和 6 位二进制加权 DAC 组成。实现高带宽时间交错 DAC 的主要挑战包括时序失配、增益失配和片间偏移,以及求和节点处负载电容的增加。

图 7. DAC 核心架构:时间交错

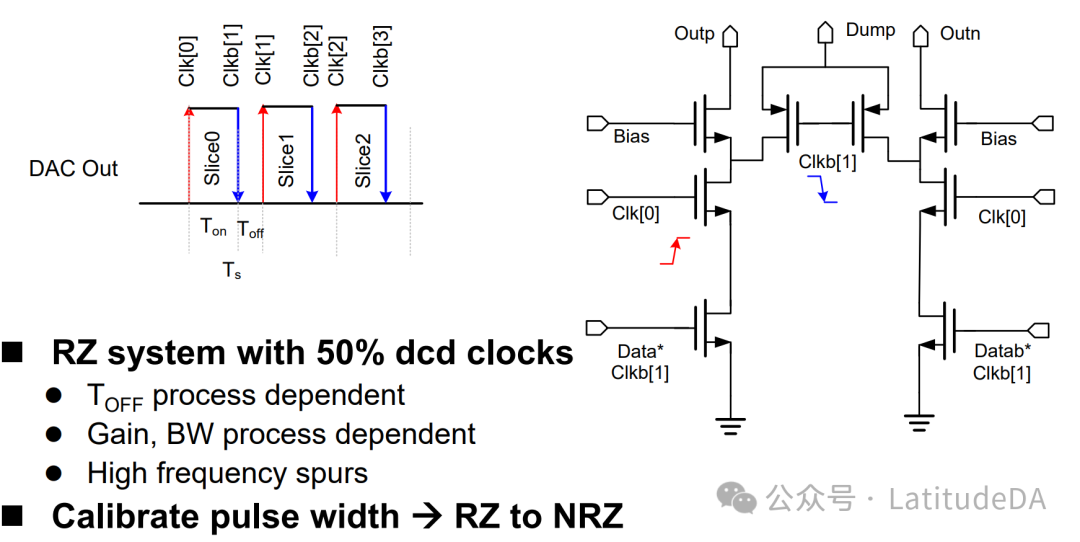

为了减轻这些损害,拟议的设计采用了多种校准技术。采用脉宽调制方案将 DAC 单元的归零 (RZ) 输出转换为非归零 (NRZ),从而提高线性度并减少高频尖峰(图 8-10)。

图 8. DAC 单元结构

图 9. 脉冲宽度校准

图 10. 脉冲宽度校准

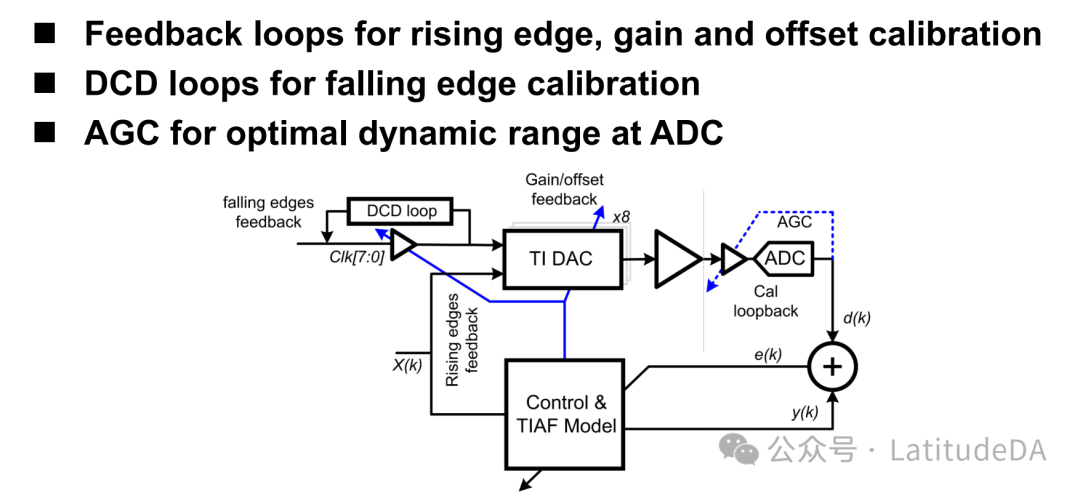

此外,还采用了基于自适应滤波器的校准方法,以解决整个 DAC 片的定时、增益和偏移失配问题(图 11)。该技术采用反馈回路来感测和校正损伤,自适应滤波器对模拟电路行为进行建模。上升沿时序、增益和偏移通过专用反馈环路进行校准,而下降沿则通过占空比失真(DCD)环路进行校准。自动增益控制 (AGC) 块可优化 ADC 输入端的动态范围。

图 11. 建议的失配校准

基于自适应滤波器的校准的主要优点包括:- 使用实际传输数据在前景或背景中运行,无需复制电路。- 使用单个传感器校准所有损伤,减少开销。 - 校准引擎可在适配收敛后关闭,从而最大限度地降低功耗。- 它为驱动器输出增加了最小的电容负载,从而保留了带宽。

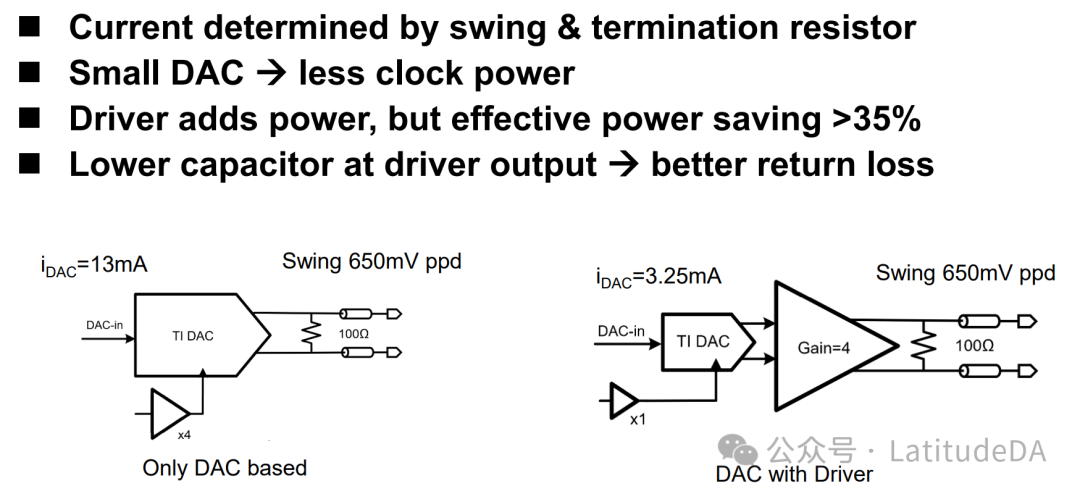

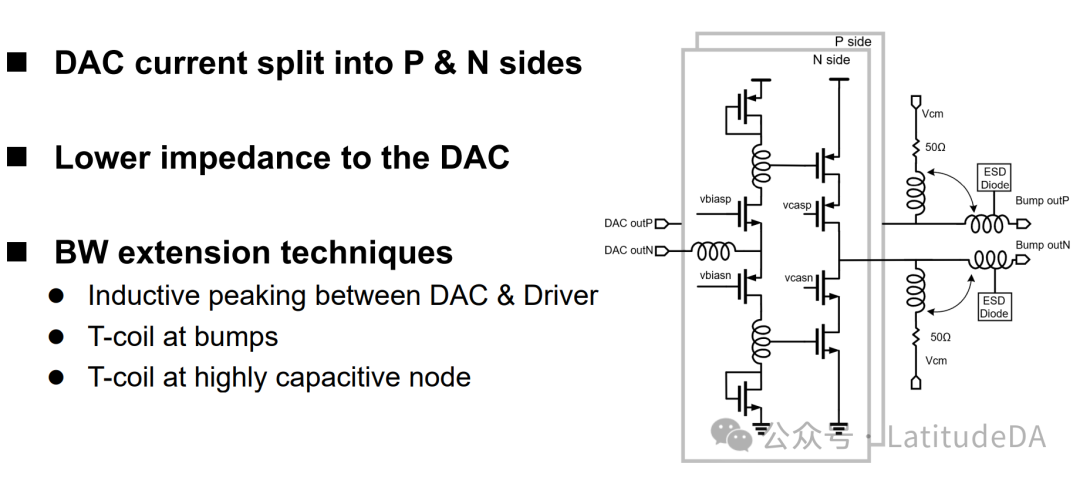

DAC 和驱动器架构为了在最大限度降低功耗的同时实现所需的高带宽,DAC 采用了低摆幅输出来驱动高带宽输出驱动器(图 12-13)。与具有较高摆幅的纯 DAC 架构相比,这种方法可节省 35% 以上的功耗。驱动器输出电容通过 DAC 和驱动器之间的电感峰值以及在高电容节点上使用 T 型线圈等技术来降低。

图 12. 带驱动器的 DAC 架构

图 13. 带驱动器的 DAC 架构

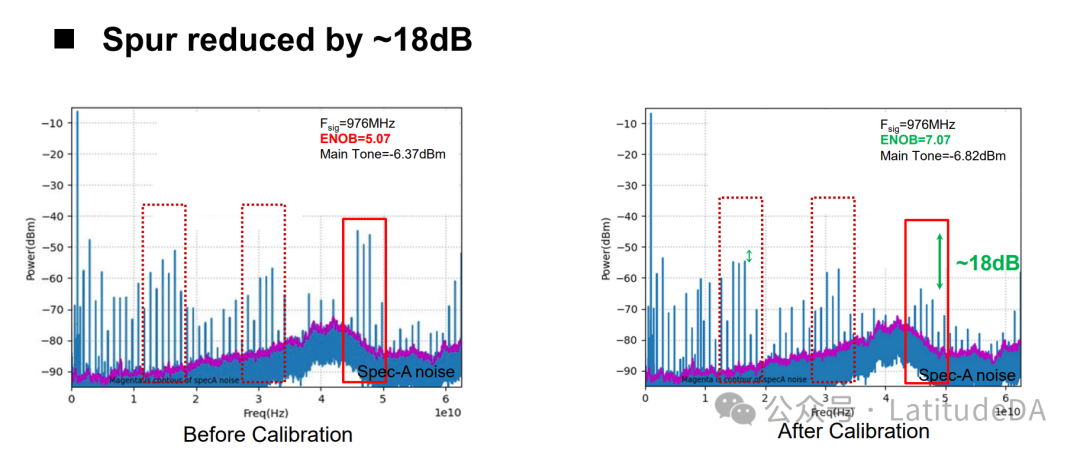

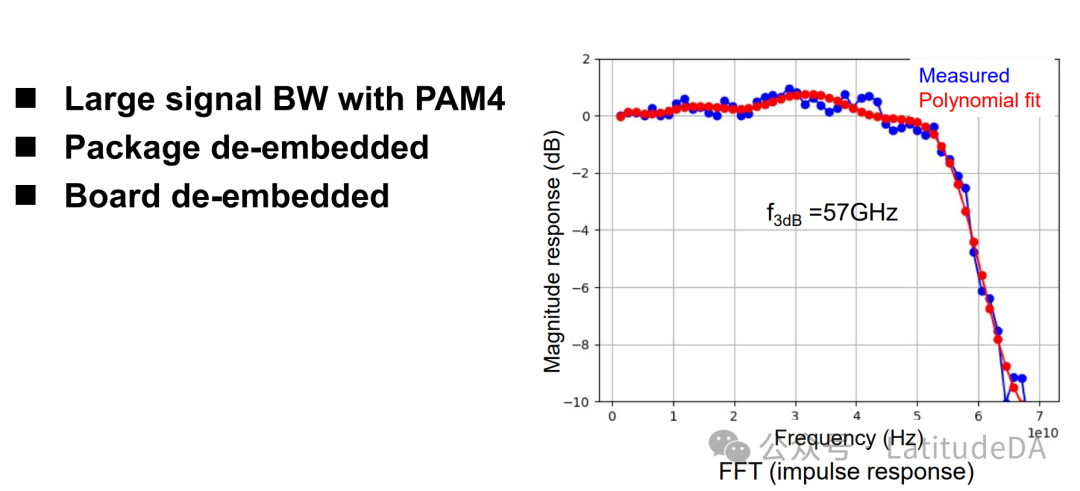

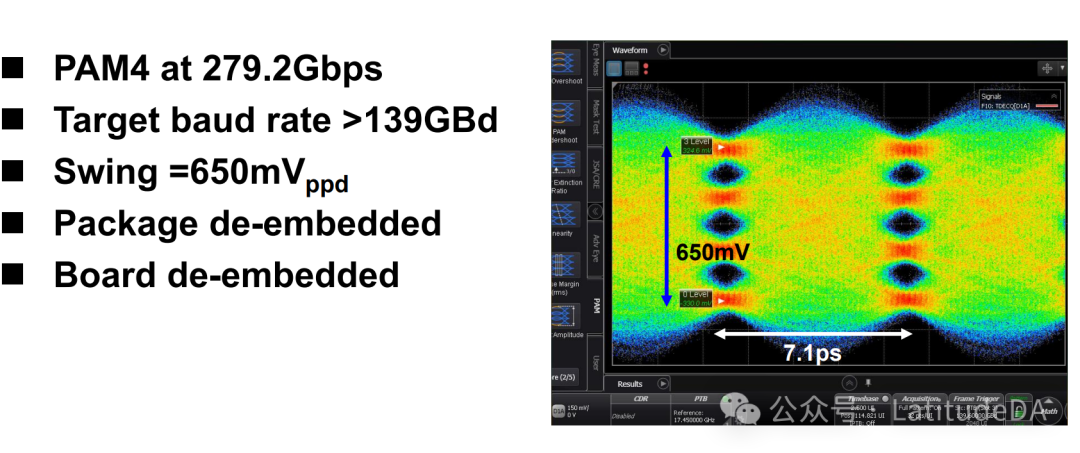

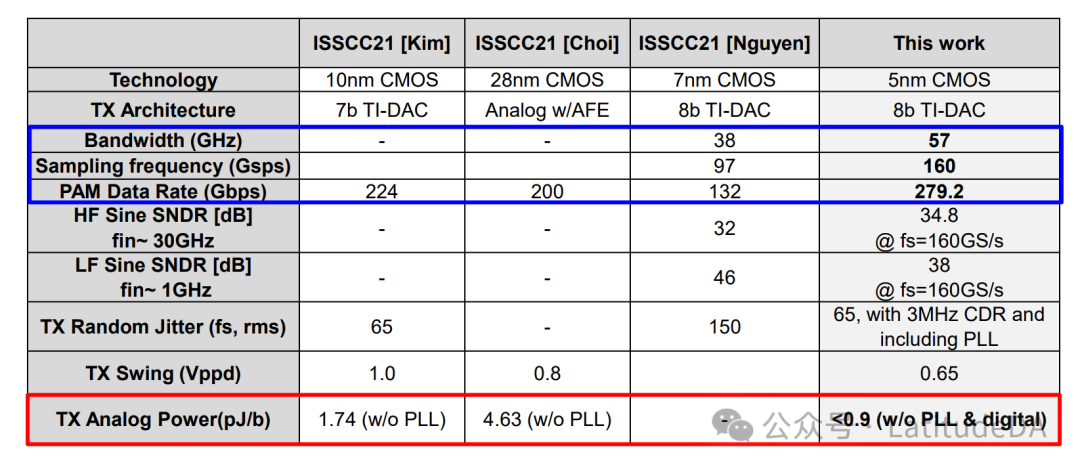

测量结果发射器采用 5nm CMOS 工艺实现,有四个发射机通道(HI、HQ、VI、VQ)和一个 PLL,占地面积为 3.8x0.86 mm2。基于自适应滤波器的校准有效地减少了 ~18dB 的尖峰,将 976MHz 时的 ENOB 从 5.07 提高到 7.07(图 14)。DAC 和驱动器的测量带宽超过 57GHz,实现了 279.2Gbps 的 PAM4 数据传输速率,摆幅为 650mV(图 20-21)。该发射器具有最先进的能效,模拟功耗低于 0.9pJ/b,不包括 PLL 和数字电路。

图 14. 测量结果

图 15. 校准测量结果

图 16. DAC 驱动器带宽测量

图 17. PAM4 眼图

表 1. 对比表

结论本文介绍了Marvell基于时间交错 DAC 和驱动器的高速发射器集成电路,设计用于下一代 800Gb/s 相干光通信系统。所提出的架构采用了新颖的校准技术,包括信道和串行器同步、脉宽校准和基于自适应滤波器的校准,以克服高带宽、低抖动和多信道同步的挑战。测量结果表明,该系统的带宽超过 57GHz,PAM4 数据传输率高达 279.2Gbps,同时模拟能效高达 0.9pJ/b。这些成果为实现高性能、高能效的相干光收发器克服障碍,使其能够支持云计算和人工智能应用日益增长的数据需求。

参考文献

[1]F. Ahmad et al., "An 8-bit 160GS/s, 57GHz Bandwidth Time-Interleaved DAC & Driver Based Transmitter with Adaptive Calibration for 800Gb/s Coherent Optical Applications in 5nm," in ISSCC 2024.

本文地址:http://www.iccsz.com//Site/CN/News/2024/03/07/20240307015912701465.htm 转载请保留文章出处

关键字:

文章标题:Marvell基于5nm工艺用于800Gbps相干光通信的发射器解说

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- · Marvell与合作伙伴在DesignCon演示200G/Lane铜链路

- · Marvell硅基光电子及异质集成技术的创新突破:面向人工智能应用的光引擎

- · LC评论Marvell分析师日:庆祝AI市场机遇

- · Marvell推出业界首款400/800G 5nm PAM4光学DSP

- · Marvell Q3数据中心业务环增20% 预计Q4环增超30%

- · Marvell加入超以太网联盟 推动AI和加速计算所需的网络增强

- · 消息称 Marvell 美满电子裁撤台湾地区 SSD 部门,据称“200 人直接团灭”

- · Marvell在OCP2023全球峰会上展示了200G电气互连技术

- · Marvell展示业界首创的AI时代高速连接解决方案

- · Marvell为可插拔模块推出业界首款800G相干DSP

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1