DARPA PIPES项目展示光学互连成果,光信号接口代替了传统电子I/O,实现传输距离和效率的大幅提升

在美国国防高级研究计划局(DARPA)“面向极端可扩展性的封装光子”(PIPES)项目的支持下,英特尔和Ayar Labs公司的研究人员展示了在使用光改善芯片互联性方面的初步进展。

通过光纤传输信号支撑了今天互联网的发展,光收发器在数据中心也无处不在,但数字系统仍然依靠电子在金属线上的移动来推动板上集成电路(IC)之间的数据。芯片封装的电信号传输的局限正越来越限制整体带宽和信号传输效率,从而影响了先进系统的性能。

PIPES项目正在探索扩大光学组件使用范围的方法,以解决这些限制问题,并使数字微电子器件达到新的性能水平。该项目的主要目标是开发具有光子接口的先进集成电路,能够在每个封装中以低于1pJ/bit的功耗驱动大于>100Tbps的输入/输出(I/O)。

2019年11月,Ayar Labs因获得DARPA PIPES项目经费支持而被选为英特尔的光I/O解决方案合作伙伴。Ayar使用硅制造技术来开发高速的、基于光学的互连“小芯片”,并使用光来替代传统的通信电子产品,将互连带宽密度提高1000倍,功耗降低10倍。

为了完成演示,英特尔和Ayar Labs的研究人员采用了DARPA另外两个项目所取得的技术进步,一是光优化嵌入式微处理器(POEM)二是通用异构集成和IP重用策略(CHIPS)。

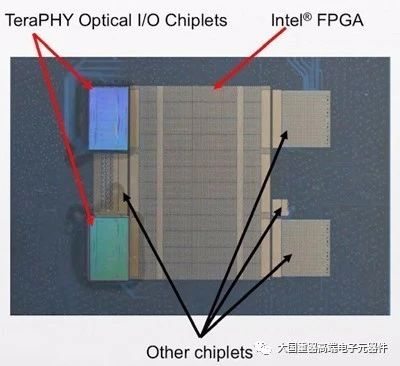

DARPA POEM项目。项目寻求开发可集成在嵌入式微处理器中的光子技术,以实现微处理器与动态随机存储器(DRAM)内部和之间的无缝、高效、高容量通信。Ayar Labs在POEM项目下的工作实现了第一个TeraPHY光学I/O小芯片。

DARPA CHIPS项目。研究人员还利用了DARPA CHIPS项目下英特尔开发的低功耗信号标准和小芯片封装工艺。为了帮助应对设计成本的快速增加和提高系统灵活性,CHIPS项目目标是开发一个离散的模块化、可重复使用的IP块生态系统,可以使用各种集成技术将其组装到系统中。该项工作的关键是建立通用接口标准,英特尔为此研发了高级接口总线(AIB)。AIB是一个公开可用的开放接口标准,使该项目下工作的Intel和其他芯片IP供应商可以轻松构建可相互操作的小芯片。PIPES团队使用AIB接口标准来集成MCM和封装内光学器件。

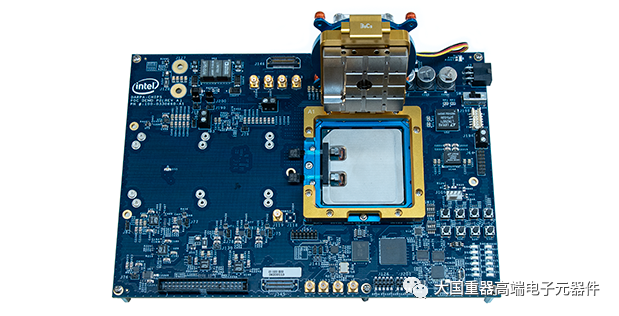

在PIPES项目的第一阶段,Ayar的TeraPHY小芯片与采用AIB接口和Intel EMIB硅桥封装的Intel FPGA共同封装,成功地用高效的光信号接口取代了先进现场可编程门阵列(FPGA)的传统电输入/输出(I/O)——电串行器/解串器(SERDES)小芯片。这些SERDES小芯片可在需要快速数据移动时补偿有限的I/O,从而实现高速通信和其他功能。

用于演示的共封装TeraPHY小芯片采用GlobalFoundries 45nm工艺制造,能够支持每秒2 Terabits(Tbps)的I/O带宽,功耗只是电I/O的一小部分。团队还利用英特尔先进的封装和互连技术,将TeraPHY和英特尔FPGA内核集成在一个封装中,创建了带有封装内光学器件的多芯片模块(MCM)。集成的解决方案通过带有直接来自FPGA的单模光纤实现高速数据链路,大大提高了互连范围、效率和延迟。

DARPA PIPES项目负责人Gordon Keeler博士说:“该初期成果展示了朝着实现可利用光信号优势的强大系统迈出了一大步。带有光接口的FPGA将产生广泛的影响,改善高性能计算、人工智能、大规模仿真和先进雷达等与国防部相关的能力。通过这次演示,英特尔团队朝着我们的目标迈出了坚实的一步。”

随着PIPES的进展,英特尔团队将继续提高集成技术的性能。在该项目的下一阶段,PIPES研究人员都将聚焦使总信号速率达到100Tbps甚至更高,使各种光子学技术日趋成熟,并满足对效率、延迟和带宽密度的苛刻要求。

本文地址:http://www.iccsz.com//Site/CN/News/2020/04/01/20200401030911384062.htm 转载请保留文章出处

关键字: 英特尔 Ayar Labs

文章标题:DARPA PIPES项目展示光学互连成果,光信号接口代替了传统电子I/O,实现传输距离和效率的大幅提升

※我们诚邀媒体同行合作! 联系方式:讯石光通讯咨询网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1