向着224Gbps速率进发的新时代

本文来自微信公众号:数据中心前沿技术

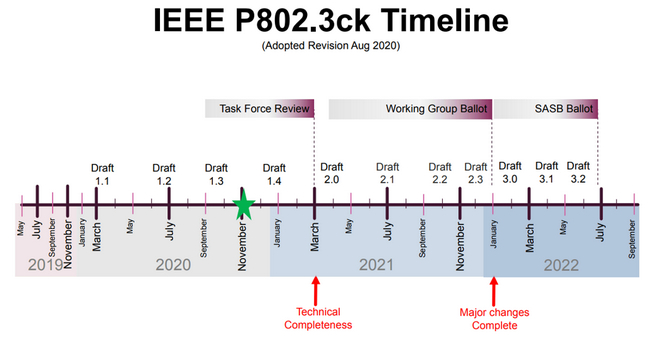

在刚刚过去的2020年12月份,Broadcom正式发布了使用112Gbps速率Serdes的两款Tomahawk4芯片,整个网络领域在2021年将会开始正式迈向112Gbps速率时代。本公众号在2019年时谈论过的这一新的速率时代,将要从今年开始逐渐落地并成为可用的产品。当然,从Broadcom 112G速率芯片的发布到我们能够看到使用这些芯片的交换机产品实物,至少还要有一年的时间。毕竟,按照IEEE 802.3CK小组的最新Roadmap,支持112Gbps速率电信号的规范要到2022上半年才会完全定稿并发布。

针对112Gbps速率的IEEE 802.3CK规范最新Roadmap

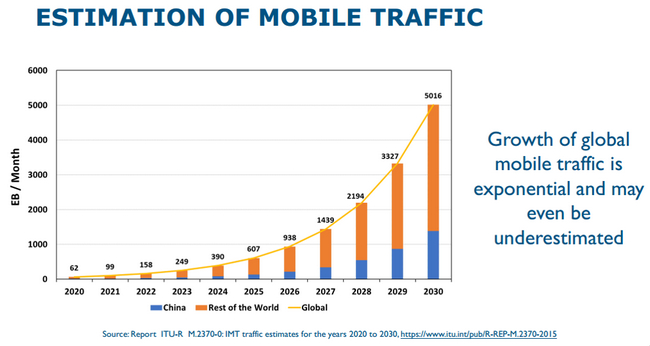

在产业界正在紧锣密鼓地为112Gbps速率系统的推出而工作时,规范领域的专家们已经把目光投向了下一代224Gbps速率标准。毕竟,在新的一个十年里,可以预见在数据中心和移动用户侧的数据流量仍然会保持指数级别的增长。于是,在2020年6月份OIF率先启动了面向下一代的CEI-224G项目,探索224Gbps电气信号的传输距离和系统架构。在这之后不久,IEEE也启动了Beyond 400Gb/s Ethernet Study Group项目,探索使用224Gbps速率的下一代以太网在技术上的可行性。从OIF和IEEE这两大国际标准组织的最新动向上可以发现,他们都认为将电和光信号速率从112Gbps升级到224Gbps是非常有必要的,但具体升级路径和方法,还需要在项目组里进行更广泛、深入的探讨。

全球移动设备流量的增长预期

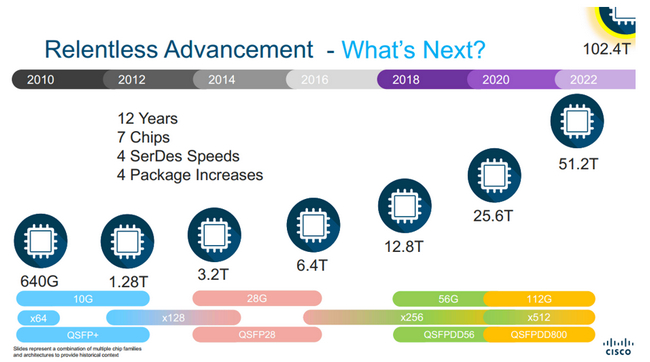

信号速率提升带来的最直接的影响就是网络芯片交换容量的增长。在2020年的时候,我们看到Broadcom、Innovium、Barefoot(Intel)、Xsight Labs等公司都推出了25.6Tbps交换容量的芯片。随着112Gbps速率的逐渐普及,网络芯片的交换容量将会在接下来的2-3年内提升到51.2Tbps。到2025年左右,102.4Tbps交换容量的网络芯片也将会进入人们的视野。

交换芯片容量的未来发展目标

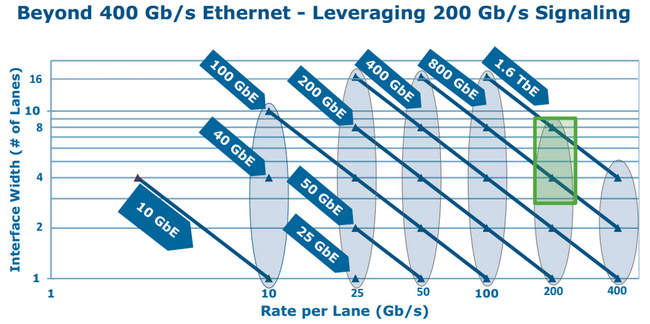

51.2T和102.4T交换容量的网络芯片在接下来的十年里先后的出现,将会推动交换机端口带宽从目前的400GbE提升到800GbE乃至1.6TbE。对于800GbE带宽的IO模块,可以由8个112Gbps通道组成。但当使用4个224Gbps通道时,IO模块可以获得更小的体积、更好的功耗和散热性能。同样的,最初的1.6TbE带宽的IO模块也可以由16个112Gbps通道构成,但这显然没有任何的应用价值。只有使用8个224Gbps通道时,IO模块在尺寸、功耗和散热等工程指标上才能满足用户设备实际应用的需求。1.6TbE带宽的IO模块未来甚至还会有采用448Gbps通道速率的可能性,当然这将会是更下一个速率时代了。

交换机端口带宽从400GbE向1.6TbE的演进方式

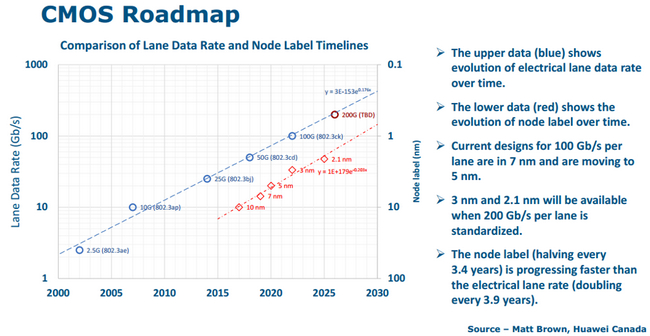

信号速率的提升对CMOS工艺制程也提出了更高的要求。在使用112Gbps通道速率的Tomahakw4-100G芯片上,Broadcom已经采用了目前最新的TSMC 7nm工艺制程。随着TSMC 5nm和3nm工艺制程在接下来的1-2年内先后成熟并商用,使用224Gbps速率的网络芯片极有可能会采用3nm工艺制程来进行设计。其实对于Serdes发送和接收电路而言,使用最新的CMOS工艺并不一定会有非常明显的功耗降低。但对于网络芯片的数据包处理逻辑电路,使用最新的工艺制程还是可以显著地降低功耗和芯片面积的。因此Broadcom、Innovium等公司未来的网络芯片也极有可能走上AMD EPYC处理器的架构之路,使用多晶片Chiplet技术来构建复杂的芯片,不同晶片模块使用不同的工艺制程。

CMOS技术与信号速率间的发展对应关系

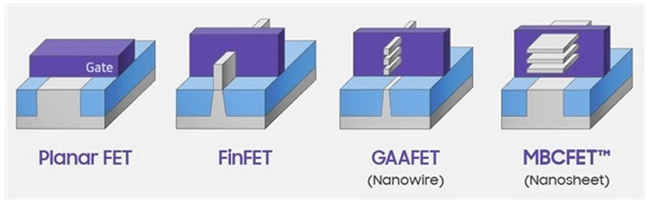

芯片工艺制程的缩减将会使得TSMC和Samsung采用更加3D化的晶体管结构。在3nm和2nm时代,三星将使用GAAFET(环绕栅极场效应晶体管),也就是纳米线(Nano wire)技术;而TSMC将使用MBCFET(多桥通道场效应晶体管),也就是纳米片(Nano sheet)技术。从纳米线到纳米片,可以看成从二维到三维的跃进,能够大大改进电路控制,降低晶体管的漏电流。按照TSMC的计划,3nm工艺制程将在2022下半年进行风险性试产,在2023年进入量产阶段。同时,2nm工艺制程将在2023下半年进行风险性试产,在2024年进入量产阶段。

3nm和2nm时代的晶体管工艺

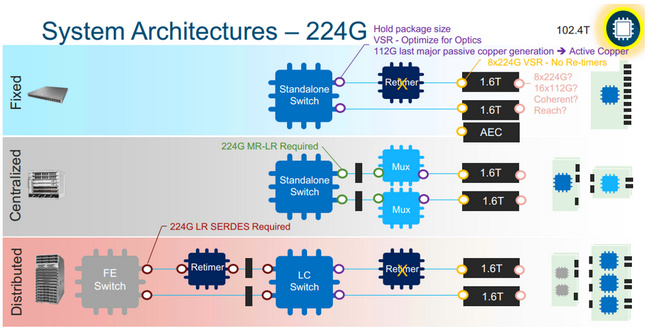

224Gbps信号速率的到来,不仅对网络芯片的设计提出了更高的要求,也将变革交换机设备的系统架构。在112Gbps速率时代,如华为这样的系统厂家已经在交换芯片与面板侧的IO模块之间使用无源电缆进行高速信号传输,从而避免使用更为昂贵的PCB板材。在224Gbps速率时代,交换芯片与面板侧的IO模块之间将会更为普遍地使用无源电缆进行连接。对于一些更长的链路,使用带有均衡器(Retimer)的有源电缆也将变得必要起来。

对于板间互联的链路,使用电信号的连接目前来看仍然会是主流方案,毕竟这样的设计方式更为成熟。但这就意味着对于224Gbps速率长距链路,需要大量地使用均衡器来进行信号中继。否则,现有的PCB和无源电缆互联方案的链路损耗将过大,无法保证信号的正常接收。因此,在进行224Gbps速率系统的设计时,设计者仍然需要VSR、MR和LR这样的国际标准作为设计指导。

224G速率时代的交换机系统架构

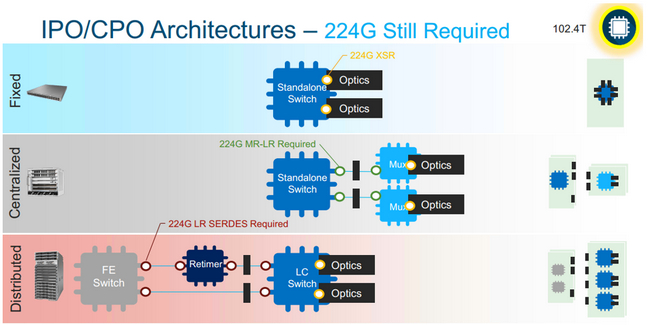

除了电缆和均衡器之外,硅光技术的应用将会是224Gbps速率时代最大的技术亮点。在2020年初的时候,Intel就已经展示了使用光电共封装技术的Tofino 2交换芯片。随着硅光技术的逐步成熟,交换芯片上将直接引出光信号,电/光转换直接在芯片内部完成。这样一来,224Gbps速率的电信号只需要在芯片内部传输很短的距离,链路损耗将不再成为电信号传输的瓶颈。在交换机IO面板侧,用户也不会再看到大量可插拔光模块的存在,这不仅可以增加交换机IO面板侧的密度,还可以大幅降低IO面板侧的功耗。到那时,采用光电共封装技术设计的交换机设备将会与市场上现有的设备在系统结构和外形上产生明显的差异。

224G速率时代交换机中的光电共封装技术

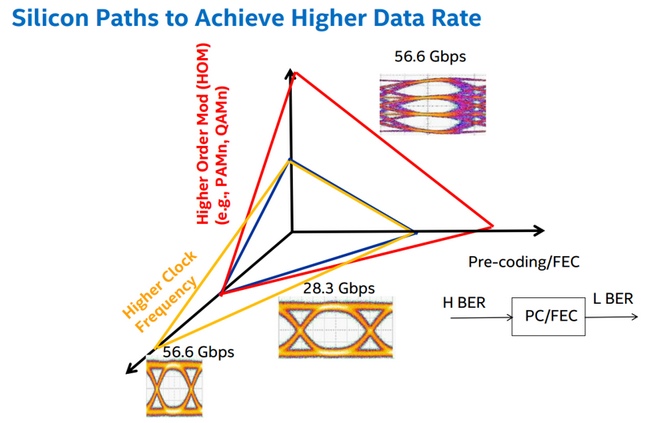

说了这么多224Gbps速率将会带来的系统架构上的变化,归根到底,这些变化还是与芯片224Gbps Serdes的具体实现方式密切相关。芯片速率升级无外乎三条路径:基频时钟的提升、更高等级的编码制式和确保信号正确接收的均衡技术。

交换芯片Serdes升级到224Gbps速率的途径

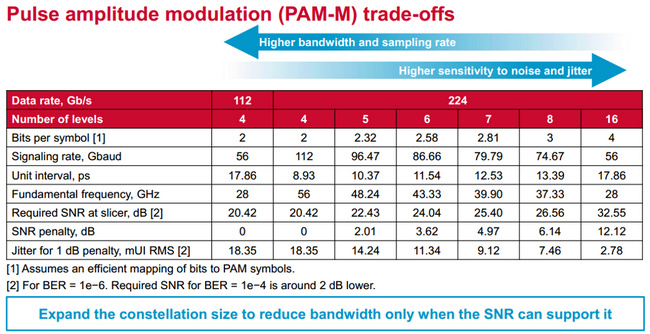

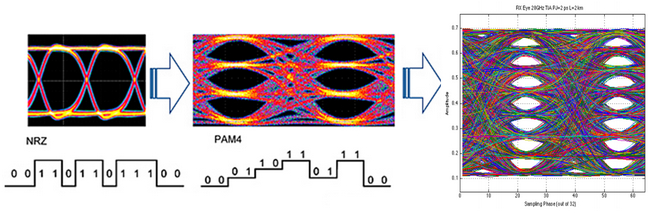

在112Gbps速率时代,为了避免信号基频提高太多,业界普遍使用了PAM4(Pulse Amplitude Modulation)信号制式。这是以太网信号从使用了几十年的NRZ(Non-Return Zero)信号制式上进行的首次变革。在224Gbps速率时代,如果继续沿用PAM4信号制式,信号基频将达到56GHz,再加上需要考虑时域信号在频域上的多次谐波,频谱带宽已经远远超出了现有的PCB材料和电缆所能支持的信号传输频率范围。于是,PAM5-PAM8,甚至更高级别的PAM16成为了224Gbps Serdes的候选对象。

不同编码制式对224Gbps速率的影响

但更高的PAM信号制式会带来更小的信噪比(SNR)裕量。从时域信号的眼图上就可以明显地看到,随着PAM制式的提升,一个完整的眼图会被分割成多个小眼图。在使用PAM8信号制式时,每个小眼图的眼睛张开度(眼高和眼宽)都会变得很小。高级信号制式不仅增加了相邻信号之间的干扰,也使得在信号接收端要有很强的均衡能力才能把受到码间干扰(Inter Symbol Interference)、抖动(Jitter)、噪声(Noise)等影响的信号正确恢复出来。

从NRZ到PAM4再到PAM8的眼图形态

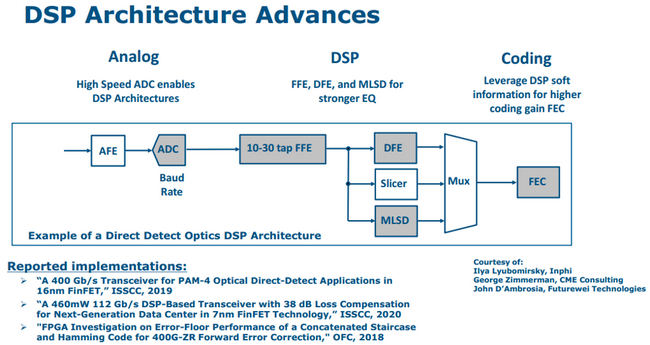

于是,我们极有可能会在224Gbps速率芯片的接收端看到使用更多阶数的前向反馈均衡(FFE:Feed Forward Equalization)和判决反馈均衡(DFE:Decision Feedback Equalization)模块,以及使用数据位上更长的连续比特数进行前向纠错(FEC:Forward Error Correction)的算法均衡。所有的这些信号接收端的均衡功能都会增加信号传输的延时,并增加芯片面积和功耗,这就又反过来要求必须采用更先进的工艺制程或新的芯片架构来设计新一代的交换芯片。

更高的信噪比(SNR)要求更强的接收均衡

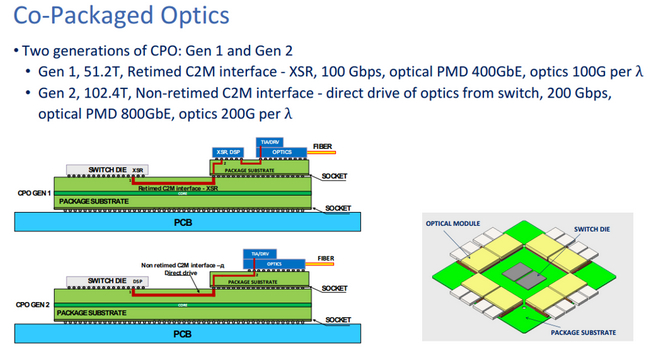

如果使用光电共封装的交换芯片,那么整个芯片设计方式都将发生变化。由于光信号在芯片内部直接转换为电信号,这就不需要电信号的发送和接收均衡能力都做得很强,从而可以有效地降低信号传输时延。在现阶段来看,光电共封装的交换芯片可以采用两步走的方式进行迭代演进。

光电共封装交换芯片的演进思路

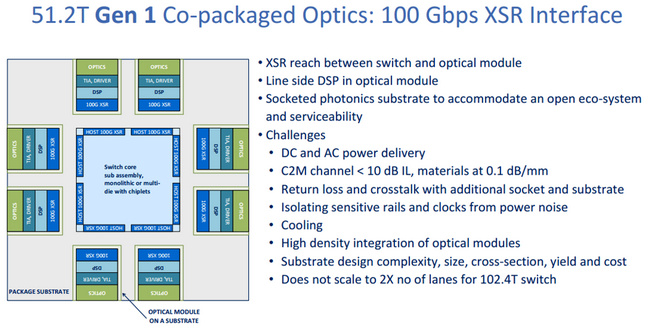

在第一代的光电共封装交换芯片里,直接把现有光模块里面的部件通过硅光技术集成到交换芯片内部,使用超短距的100G-XSR电信号接口连接两部分电路,芯片封装上引出的光纤则直接输出100Gbps波长的光信号。

基于100Gbps XSR接口的第一代光电共封装芯片

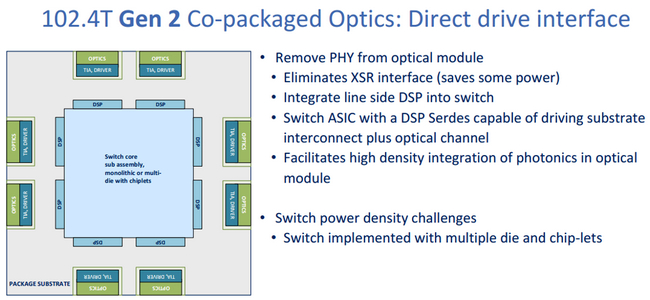

在第二代的光电共封装交换芯片里,将进一步地把光模块部件里的PHY模块(100G-XSR接口和DSP模块)集成到交换芯片内部,光接口部分只保留光电转换和光发送/接收模块。这样一来,就可以在芯片核心Die的外围集成更多的硅光模块,从而实现102.4Tbps这种更高的交换带宽。

基于DSP技术的第二代光电共封装芯片

当然,不论是第一代还是第二代光电共封装的交换芯片,都面临着供电、散热、Chiplet设计技术、加工良率等各种工程问题上的挑战,实现起来并不容易。但随着技术的不断进步,相信这些工程问题在未来的3-5年内一定会得到解决。

总 结

站在新的一个十年的开端,必然会展望未来技术发展的方向。112Gbps速率在接下来的2-3年内会逐渐成为网络领域的主流。而作为其下一代的224Gbps信号速率,已经开始崭露头角,将会是未来各种展会、论坛上的热门话题。不论是OIF还是IEEE,对224Gbps速率的研究都还在起步阶段,随着时间的推移,相信会有更多准确的分析结论和更新的设计方案被提出。本公众号会继续跟进,及时给大家带来业界最新的研究成果。

在224Gbps速率时代,出于成本上的考虑,无源电缆和有源电缆将会在网络设备的系统设计中发挥更大的作用。在本文中对这一话题只是简单涉及了一下,后面将会专门写一篇文章,探讨一下224Gbps速率时代铜退光进的光电模块。敬请期待!

本文地址:http://www.iccsz.com//Site/CN/News/2021/01/15/20210115012755027563.htm 转载请保留文章出处

关键字: 224Gbps

文章标题:向着224Gbps速率进发的新时代

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1