数据中心大带宽技术分析与国际标准化进展

1 业界需求

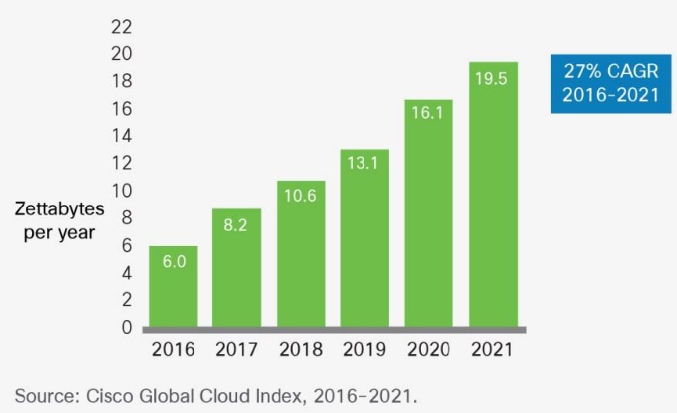

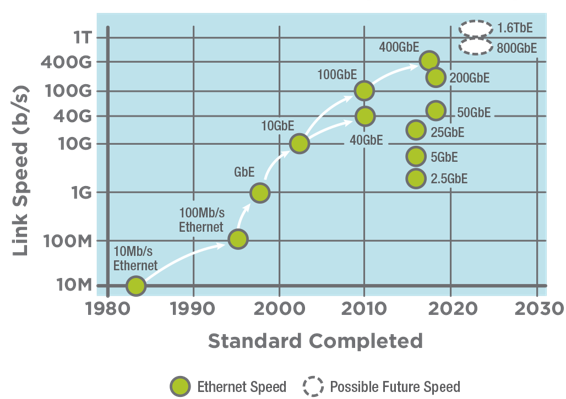

随着AI,大数据,分布式存储和计算等业务的飞速发展,数据中心对高吞吐和大带宽的要求越发迫切。思科2018年发布的GCI指数显示,数据中心内流量保持每年约30%的增长,到2021年将达到约20 Zettabytes。当前100G已在数据中心内海量使用,400G预计在2019 ~2020年开始部署。2019年以太网联盟发布的以太网路标显示,2022年后将逐步进入800G/1.6T 时代。

图1. Cisco Global Cloud Index, Cisco, 2018

图2. Ethernet Roadmap, Ethernet Alliance, 2019

随着400G产品的日趋成熟,800G的技术方向也逐渐明确。

1) 芯片:博通于2017年发布了12.8T的Tomahawk 3 芯片, 支持32个400G端口。预计2022年将会出现50T+的大容量芯片,支持64个800G端口以及最新的112G SerDes技术。

2) 光模块:2018年起,各大主流模块厂商陆续发布400G模块产品。当前400G模块支持光口速率单波长100G(多模除外);后续当SerDes升级到112G, 光口速率将匹配电口速率,模块将自然演进到8*100G。

3) 系统:2018年,思科、Arista、华为均发布了基于12.8T芯片的TOR交换机,支持32个400G端口,采用QSFP-DD或OSFP封装。这两种封装格式都支持后续演进到800G。

2 技术趋势

根据以太网速率和物理层标准的发展历史,以及相关技术、器件的成熟度,我们预测,800G第一代将会以8*100G(单通道100G)为主。以下章节我们将从模块、芯片、系统和封装技术等方面对800G互联的技术趋势展开讨论。

2.1 多模提速

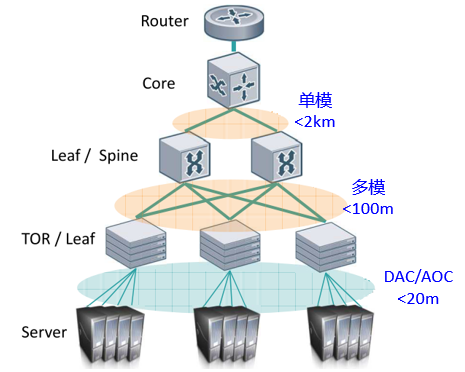

图3. 数据中心CLOS架构和互联

图3 展示了数据中心主流的CLOS组网架构和各层设备间的互联关系。直连电缆(DAC)和有源光缆(AOC)用于Server和TOR交换机之间的互联,覆盖20米以下的距离;AOC一般采用低成本的多模模块和多模光纤。多模同时部署在TOR上行和spine交换机之间,覆盖100米以下的距离。Spine上行,由于互联距离较长,一般使用单模覆盖,并通过波分技术(如CWDM)实现单纤传输,降低互联成本。

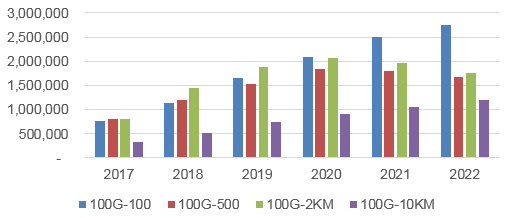

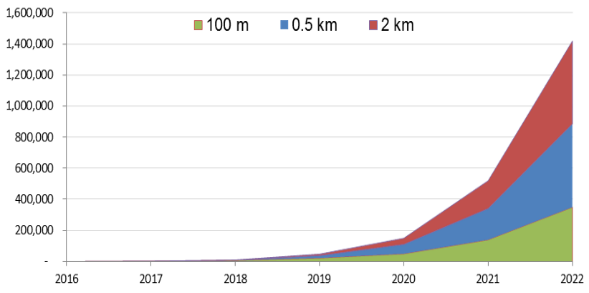

由于巨大的成本优势,多模模块和多模光纤在数据中心内海量使用。从LightCounting 2018年发布的光模块发货量趋势来看(图4),100G多模不断上升,到2022年达到顶峰;400G多模100米、单模500米和2km三分天下。

图4:100G & 400G光模块发货量预测,LightCounting,2018

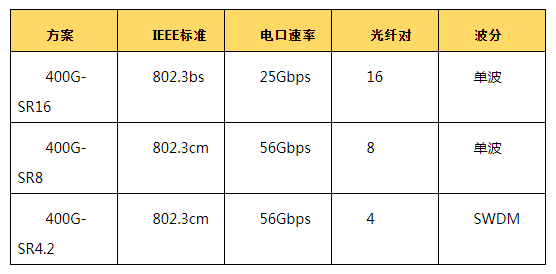

表1 展示了IEEE定义的400G多模标准:400G-SR16,400G-SR8和400G-SR4.2。400G-SR16 基于电口25G-SerDes, 需要16路光电器件,MPO-32连接器以及16对光纤。由于缺少用户和模块厂商的支持,该标准在业界没有被广泛应用。400G-SR8和400G-SR4.2标准基于电口56G-SerDes, 器件和光纤数减半;而400G-SR4.2采用了短波分复用技术(SWDM),实现了单纤双向,可以复用100G时代的4对纤部署。随着大带宽VCSEL器件的成熟以及DSP技术的加持,多模有望在800G时代继续演进。

表1:IEEE 400G多模标准

2.2 封装格式

图5:Intel光电集成路标:可插拔模块à在板光模块à光电合封,Intel, 2018

随着电口速率提升到112G,高速信号在PCB传输中的损耗也随之增大。为了驱动交换芯片到光模块的PCB走线,满足信号完整性,SerDes可能需要使用相对复杂的DSP。这将造成芯片整体功耗大幅增加。

为了解决功耗限制,如图5所示,业界普遍的做法是将光模块不断向交换芯片靠近,从而缩短芯片和模块间的走线,即SerDes的驱动距离。在板光模块和光电合封技术应运而生。业界有观点认为,到2025年,可插拔光模块和无源铜缆将逐渐被以上两种技术取代。

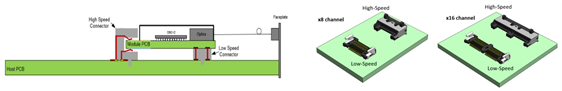

图6:在板光模块电接口和连接器示意图

在板光模块或者嵌入式光引擎的概念并不新鲜,Finisar的SNAP系列和Avago的POD系列等早在十多年前就已进入市场。这些产品均属于私有或定制化方案,可支持12路VCSEL,并集成在PCB板上,为集群提供高速高密的框内互联。随着数据中心客户和业务的增长,业界呼唤标准化方案的出台。2013年,微软提出传统可插拔模块面临功耗和密度问题,在后400G时代将选择在板光模块作为技术方案。同年,微软联合思科、博通、Finisar等14家厂商成立COBO联盟,旨在提供标准化的在板光模块方案;当前成员已经超过70家。2018年,COBO发布技术规范(如图6所示),定义了8路和16路的客户侧电接口、OBO连接器规格以及热参数,支持可插拔的在板光模块形态。当前标准最高支持800G,未来可演进至1.6T。

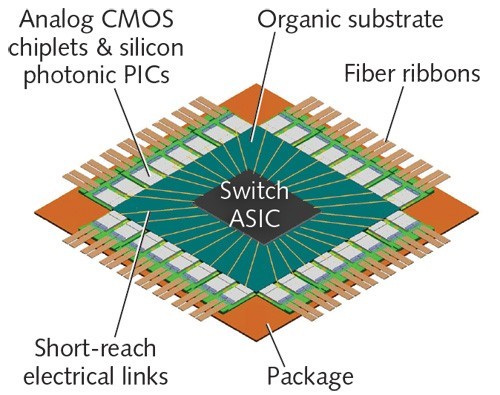

光电合封,将光引擎和交换芯片封装在一个衬底上。相比在板光模块,合封后,SERDES IO和光引擎的距离进一步减小到毫米级,交换芯片的功耗大幅减低。合封后的芯片直接扇出光纤,交换机前面板不再受传统模块封装格式的限制,可以采用尺寸更小的MPO连接器(此处有图)实现高密高速互联。预计单槽位将可支持上百T的容量,是现有可插拔模块可支持容量的10倍以上。

图7 光电合封示意图

图 8.光电合封概念样机,Luxtera @ OFC 2018

业界普遍认为光电合封是大带宽接口形态的必然趋势,模块、系统和线缆厂商也纷纷合作并推出样机。2018年OFC,Luxtera展示了51.2T的光电合封样机。如图 8所示,该样机采用了4个外置光源,驱动4个光电合封引擎,每个引擎支持12.8T的容量,面板采用MPO连接器扇出光纤。

2019年3月,微软和Facebook联合成立了Co-Packaged Optics (CPO) 协作项目。该项目聚焦用户视角,为光电合封方案提供系统级需求,并针对电接口、模块管理、芯片封装等制定端到端的开放标准。该项目的成立表明了数据中心主流用户对于光电合封作为下一代互联技术方向的认可,以及对获得产业链支持的渴望。光电合封涉及到产业链的各个环节和不同厂商,需要从接口定义、封装、测试等各方面紧密合作和推动标准化。

2.3 大容量芯片

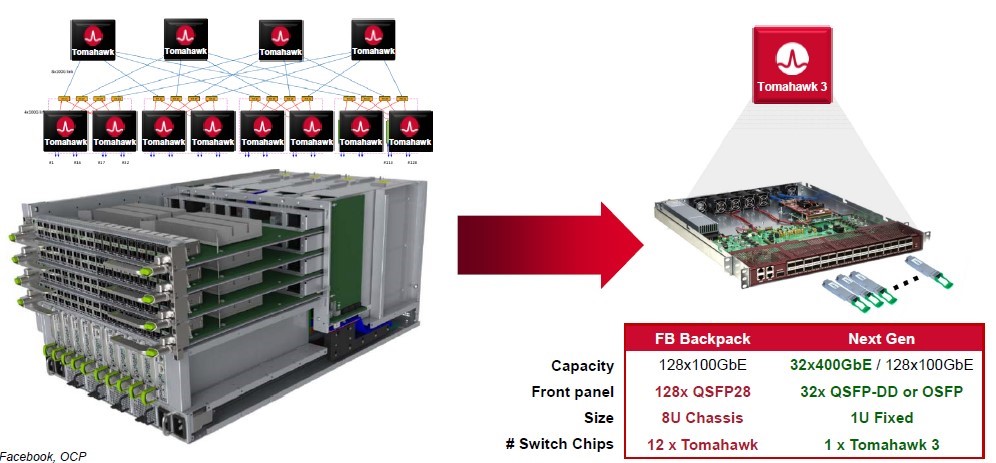

随着数据中心内业务的发展,流量的激增,用户对于大带宽网络设备的需求越来越迫切。用户侧和网路侧交换机的容量在10年间增长超过50倍。决定系统容量的主要因素就是芯片容量。在单芯片容量受限的情况下,利用多芯片scale-out的方式可以构建大容量的系统,传统框式交换机便是这样的思路。如图9所示,Facebook 2016年发布的 Backpack框式交换机,利用12片3.2T Tomahawk 芯片(4块线卡,4块交换卡),实现了12.8T的交换容量。随着12.8T的 Tomahawk 3单芯片的发布,一个单槽位(1RU)的盒式交换机就可以实现12.8T。相比Backpack, 功耗和成本都降低了80%以上。当互联速率提升至单通道112G,传统框式结构面临功耗散热等诸多工程工艺的瓶颈,继续演进面临巨大挑战。因此,基于大容量盒式交换机的scale-out架构将成为数据中心架构和设备形态的一大趋势。国内外多家数据中心用户已经开始了 ”盒替换框” 的进程。大容量盒子的关键就是大容量芯片。

图9: 8U-12.8T-框式交换机 Vs. 1U-12.8T-盒式交换机

https://www.nextplatform.com/2018/01/20/flattening-networks-budgets-400g-ethernet/

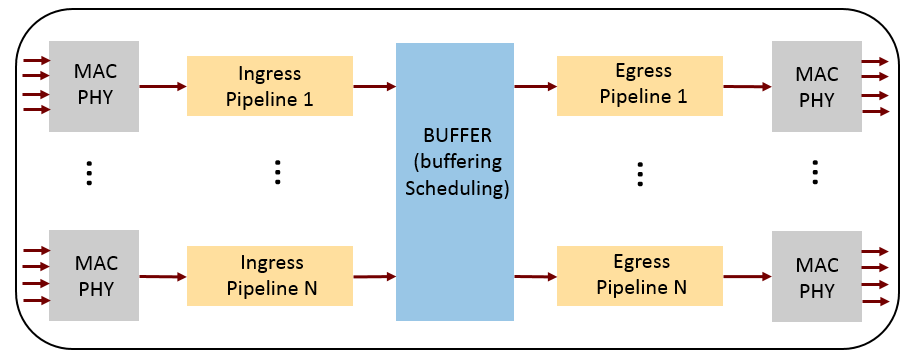

大容量芯片在实现中面临诸多挑战,其中一个限制就是芯片Die面积的约束。图10展示了交换芯片的内部架构。芯片die size增大导致良率降低、成本上升。减小芯片面积的一个直接方式是升级工艺制程。CMOS制程大概每三年更新一代,2019年7nm工艺已经成熟,产品陆续发布。5nm工艺已在研发中,未来将会向3nm继续演进。从16nm到5nm的演进过程中,PPA (Performance, Power, Area) 以及成本收益逐渐放缓,新制程在综合性能上的提升不大。虽然工艺升级可以给芯片面积带来部分收益,但大容量芯片仍然面临die size受限,单个die无法实现的巨大风险。

图10: 交换芯片内部架构

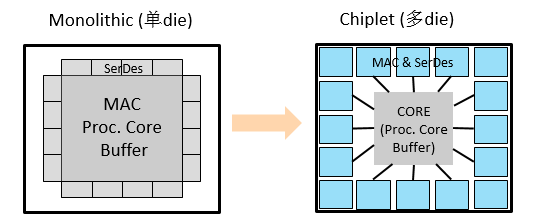

图11:单Die架构 Vs. Chiplet多Die架构

Chiplet对芯片进行解构,突破了芯片面积的物理瓶颈,是解决die size问题,实现大容量芯片的一个重要途径。Chiplet架构将芯片按功能划分为多个子芯片,各自独立成die。由于每个die的面积变小,单片晶圆上可摆放的Die数目增加,良率提升,成本下降。不同die可使用不同工艺,容量升级时只需升级部分模块/die, 加快了大容量芯片的迭代。同时,Chiplet架构下,热源分散,更利于散热。Die间互联接口、多Die集成封装是Chiplet架构下要解决的关键问题。

(a) (b) (c)

图12: (a) Barefoot Tofino-2 Chiplet架构; (b) Marvell 12.8T test chip in MCM; (c) Intel EMIB封装和AIB接口

Chiplet是未来大容量芯片架构的一个重要趋势。但还有诸多问题和挑战有待业界共同探讨和解决:比如,采用异构还是同构架构;同构架构下,多Die间的负载分担,如何保证线速转发;如何进一步提高die间互联带宽;多Die间的流量控制和资源配置,如何提高内存利用率,实现无损不丢包。

3 国际标准化进展

2019年,ODCC联合了20多家国内光互联产业链会员,成立了下一代数据中心互联项目(DCCNG),并于2019开放数据中心峰会发布《DCCNG:下一代数据中心互联白皮书》,白皮书旨在牵引我国数据中心下一代互联产业链在技术、规范和产品各个方面的探讨,一经发布就受到了业界广泛关注。同时,ODCC代表我国数据中心产业伙伴,将2019开放数据中心峰会最新发布的DCCNG相关成果带到IEEE802进行了推动,得到了业界同行的高度认可。DCCNG成果最终被IEEE802.3官方正式采纳,对立项成功起到了重要支撑作用!

IEEE802.3作为定义物理连接的国际标准组织,于今年也开展了相关技术的立项研讨。ODCC代表中国数据中心互联产业,积极投身参与到国际标准的立项工作中。ODCC相关专家联合华为等业界伙伴,针对多模单波100G互联方向,在IEEE802.3进行了历时数月的多轮宣讲,其对我国光互联产业发展需求的调研以及相关技术的思考,得到了IEEE802.3官方的高度认可。本次IEEE802全会对该方向进行了立项投票,通过并正式立项。此次立项开启国际单波100G多模标准的制定工作,牵引和推进产业链解决100G PAM4多模传输的技术难点,催熟相关芯片研发和成熟度,支撑下一代基于112G SerDes IO的服务器100G接入和交换机互联低成本方案。

本文地址:http://www.iccsz.com//Site/CN/News/2020/04/29/20200429030741402303.htm 转载请保留文章出处

关键字: 数据中心

文章标题:数据中心大带宽技术分析与国际标准化进展

※我们诚邀媒体同行合作! 联系方式:讯石光通讯咨询网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1