台积电布局3DBlox 推动3DIC技术新进展

ICC讯 在2024年台积电OIP生态系统论坛上,台积电的一个技术讲座重点讨论了如何最大限度地提高3DIC(3D集成电路)的设计效率。随着半导体技术的快速发展,3DIC已成为提高芯片性能、能效和密度的下一个前沿领域。台积电一直致力于简化这些尖端解决方案的设计流程,而3DBlox正是这一使命的核心。3DBlox是台积电推出的一个创新框架,包含标准化设计语言,旨在解决3DIC设计的复杂性。 以下是台积电3DIC方法小组副总监Jim Chang的演讲综述。

2022年~2023年的进展:为3DBlox奠定基础

2022年,台积电开始探索如何展示其3DFabric产品,特别是CoWoS(基板上晶圆芯片封装)和INFO(集成扇出型封装),它们是3DIC的关键技术。CoWoS使用硅中介层集成芯片,而INFO则使用RDL(再分布层)中介层。台积电将这些方法结合在一起,创造出CoWoS-R和CoWoS-L,前者用RDL技术取代硅中介层,后者则集成了本地硅互连。

有了这些构件之后,台积电意识到他们需要一种系统的方法来表示其日益复杂的技术产品。这促成了3DBlox的诞生,它为表示台积电3DFabric技术的所有可能配置提供了标准结构。通过专注于三个关键要素——芯片、芯片接口和接口之间的连接,台积电能够有效地模拟各种3DIC配置。

到2023年,台积电已在芯片再利用和设计可行性方面进行了深入研究,为早期设计探索引入了一种自上而下的方法。这种方法使台积电及其客户在获得所有设计细节之前,就能进行早期电气和热分析。台积电通过一个允许芯片镜像、旋转或翻转,同时保持芯片信息主列表的系统,开发了一种简化的方法来检查多个芯片的设计规则。

2024年的创新:利用3DBlox克服复杂性

到2024年,台积电将面对3DIC系统日益增长的复杂性,并制定新的战略来解决这一问题。关键的创新是将三维设计挑战分解为更易于管理的二维问题,重点关注总线、TSV(硅通孔)和PG(电源/地线)结构。这些元素一旦在三维平面规划阶段定位,就会转化为二维问题,利用现有的二维设计解决方案简化整个流程。

2024年的关键技术发展

台积电2024年的重点是最大限度地提高3DIC设计效率,主要围绕五个发展领域:设计规划、实施、分析、物理验证和基板布线。

(1)设计规划:管理电气和物理限制

在3DIC系统中,放置总线、TSV和PG结构需要同时注意电气和物理限制,尤其是电迁移和IR(EMIR)限制。芯片间的功率传输必须精确,PG结构在为其他设计元素节省物理资源的同时,还能维持必要的功率。

台积电的关键创新之一是将单个TSV实体转换为密度值,从而可以对其进行数值建模。通过使用Cadence Cerebrus Intelligent Chip Explorer和Synopsys DSO.ai等人工智能驱动引擎,台积电能够探索解决方案空间,并反向映射总线、TSV和PG结构的最佳解决方案。通过这种方法,设计人员可以为其特定设计选择最佳折衷方案。

此外,2024年还强调了芯片与封装的协同设计。台积电与主要客户合作,共同应对芯片和封装团队之间的协调挑战,这两个团队以前是独立运作的。通过使用3DBlox的通用对象格式和通用约束,团队可以更高效地协作,在流程早期,甚至在技术文件可用之前解决设计约束。

(2)实施:加强重复使用和分层设计

随着客户要求提高芯片复用率,台积电在3DBlox语言中开发了分层解决方案,以支持不断增长的3DIC设计。随着对齐多个芯片所需的对准标记数量不断增加,台积电与EDA合作伙伴密切合作,确定了四种主要类型的对准标记,并将其自动插入到布局与绕线流程中。

(3)分析:解决多物理场相互作用问题

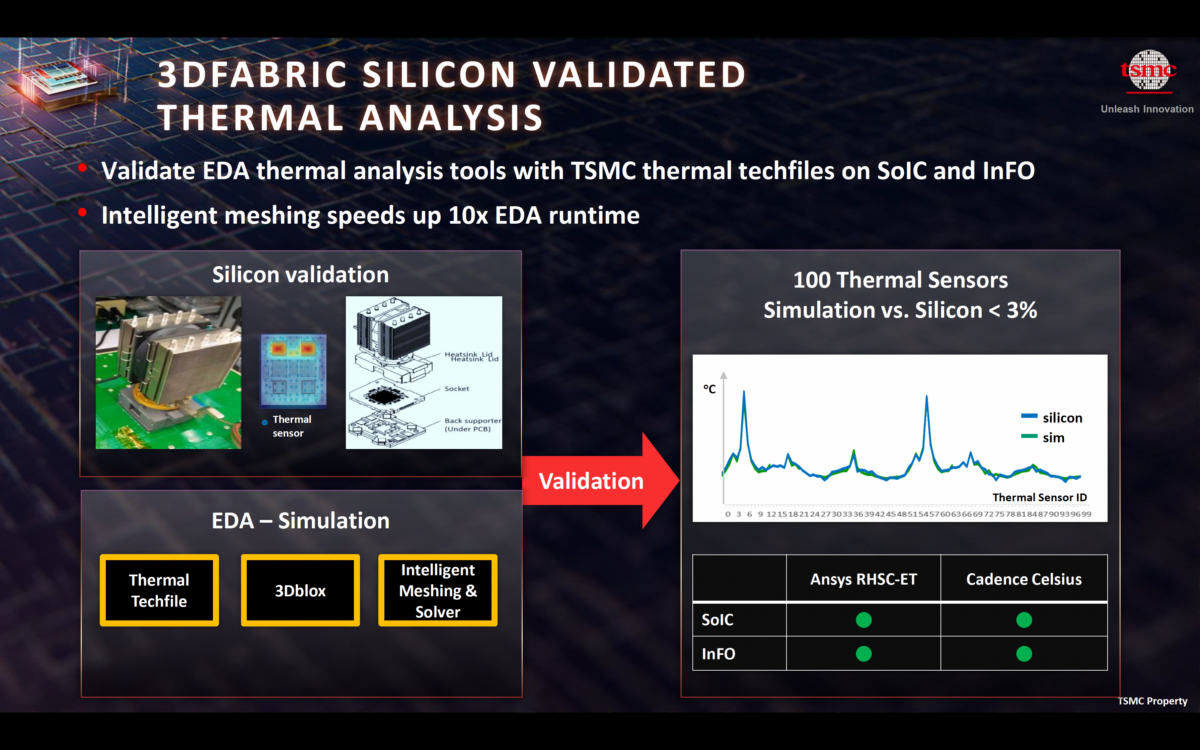

在3DIC设计中,多物理场相互作用(尤其是与热问题有关的相互作用)变得更加突出。台积电认识到,由于不同物理引擎之间的耦合效应更强,因此3DIC中的热问题比传统2D设计中更为突出。为解决这一问题,台积电开发了一个通用数据库,允许不同的引擎根据预定义的标准进行交互和会聚,从而实现对设计空间的有效探索。

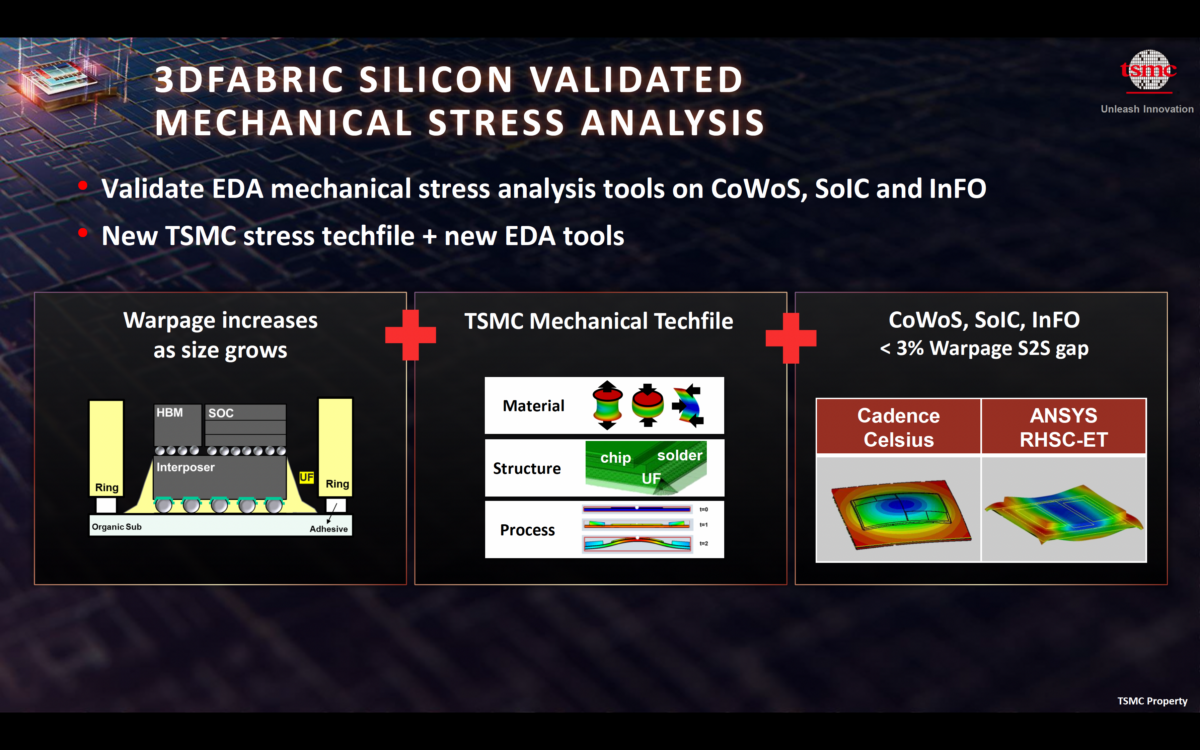

2024年推出的关键分析工具之一是翘曲分析,这对3DIC结构尺寸的增长至关重要。台积电开发了Mech Tech文件,为行业合作伙伴定义了促进应力模拟的必要信息,填补了半导体行业在翘曲解决方案方面的空白。

(4)物理验证:确保3DIC设计的完整性

台积电解决了天线效应这一制造问题,金属可能积累等离子电荷,这些电荷可通过TSV和凸点穿透栅极氧化物。通过与EDA伙伴合作,台积电创建了一个设计规则检查 (DRC) 平台,可对天线效应进行建模和捕捉,确保在设计过程中考虑到天线效应。

2024年,台积电还推出了针对3DIC系统的布局与原理图 (LVS) 验证增强功能。在此之前,LVS层采用一顶一底的芯片配置。然而,3DBlox全新的自动生成工具可准确验证任何配置,支持更复杂的多芯片设计。

(5)基板布线:应对日益增长的复杂性

随着3DIC集成规模的扩大,基板布线的复杂性也在增加。基板设计历来是一个手动过程。基板尺寸的不断扩大,加上现代3DIC设计的复杂要求,使这一领域必须进行新的创新。

台积电三年前开始研究Interposer Substrate Tech文件格式,到2024年,他们已经能够对高度复杂的结构进行建模,例如在模型中包含泪滴形结构。这一进步更准确、更详细地展示了基板,对于3DIC领域出现的更大型、更复杂的设计至关重要。台积电通过3DFabric联盟与OSAT伙伴合作支持这种格式。

总结:3DBlox——为3DIC创新铺平道路

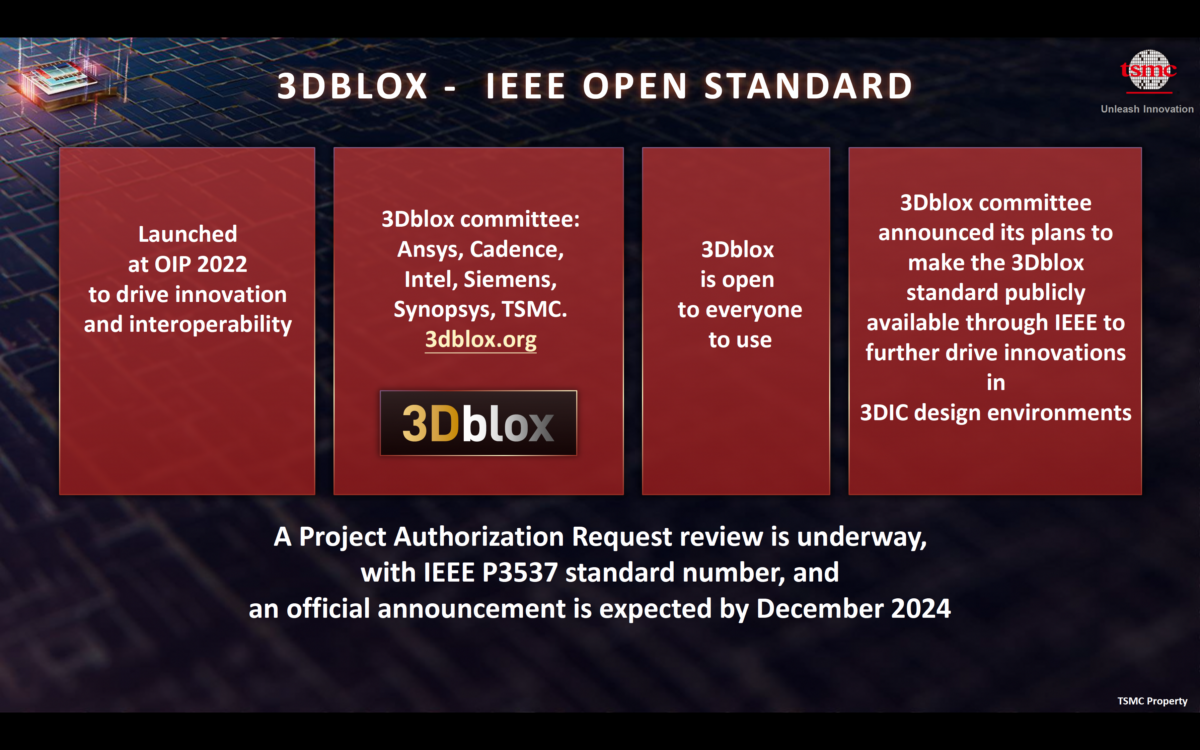

台积电公司的3DBlox框架已被证明是管理3DIC设计复杂性和规模的关键一步。从2023年的早期探索和设计可行性,到2024年在设计规划、实施、分析、物理验证和基底布线方面的突破,台积电的创新正在为更高效、更可扩展的3DIC解决方案铺平道路。随着业界向更先进的3D集成迈进,3DBlox委员会宣布计划通过IEEE公开发布3DBlox标准。未来几年,3DBlox将继续发挥重要作用,帮助设计人员满足半导体技术日益增长的需求。

本文地址:http://www.iccsz.com//Site/CN/News/2024/10/10/20241010023650659205.htm 转载请保留文章出处

关键字:

文章标题:台积电布局3DBlox 推动3DIC技术新进展

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- · 台积电美国厂试产5nm AMD成第二大客户

- · SEMI硅光子产业联盟成立,台积电及日月光等30多家企业加入

- · 台积电首座欧洲晶圆厂 8 月 20 日举行动土典礼,规划月产能达 4 万片

- · 消息称英特尔挖角台积电工程师,芯片代工竞争加剧

- · 台积电:台湾地区高雄楠梓产业园在建2nm晶圆厂未受台风“格美”影响

- · 台积电获英特尔下一代AI芯片订单 将采用3nm制程及CoWoS封装

- · 台积电6/7nm制程2025年初起降价10%

- · 台积电进一步扩产 CoWoS ,消息称考虑在台湾地区云林县建设先进封装厂

- · 消息称台积电 3/5 nm 制程明年涨价:AI 产品涨 5~10% ,非 AI 产品 0~5%

- · 台积电南京已获美国商务部VEU授权

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1