光电共封装芯片在系统应用中的展望

作为业界技术热点,光电共封装技术在过去的几年里一直是谈论较多的话题。在2020年初的时候,Intel展示了应用硅光技术实现光电共封装的首款交换芯片。本公众号也根据业界已有的调研数据,介绍了硅光技术的现在和未来。随着时间进入2021年,IEEE和OIF这两大国际标准组织先后成立了工作组,开始研究下一代224Gbps速率系统。在向着224Gbps速率进发的新时代,光电共封装技术成为了实现更高速率、更大带宽、较低功耗的网络和计算芯片的一条必由之路。随着业界对光电共封装技术研究的深入,对其具体实现方式有了多种方案。虽然目前真正使用光电共封装技术的网络和计算芯片还很稀少,但我们已经可以展望一下在接下来的几年里会出现的光电共封装芯片的形态,以及这一前沿技术可能会带来的工程挑战。

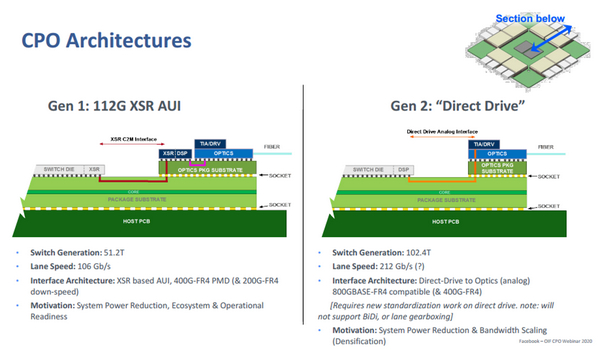

在探讨224Gbps速率系统的实现途径时,曾经提到采用硅光和光电共封装技术芯片的两种设计方案。一种是交换芯片Die上引出短距的XSR接口,通过XSR接口与芯片基板上的光部分进行电气互连,用于信号调制的DSP部分与光部分放在一起。另一种则是将DSP部分进一步集成到交换芯片Die上,从而简化芯片基板上的光部分,降低芯片内部光部分的功耗。

采用光电共封装技术的芯片架构

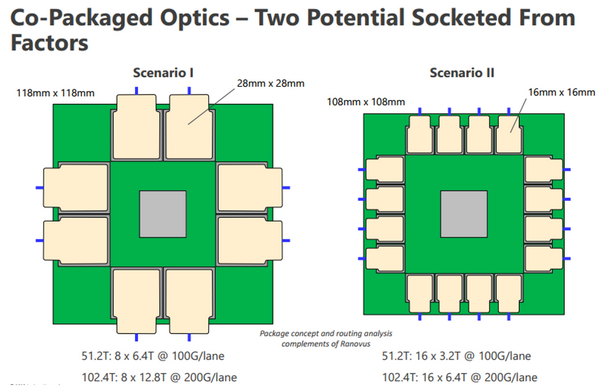

不论采用哪种方式,都意味着在芯片内部基板上核心Die的四周要放置一圈光电转换模块。根据现有交换芯片的大小,如果采用较大尺寸的光电转换模块,只能放置8个;如果将每个大的光电转换模块分成两个小模块,则可以放置16个。于是,对于51.2T交换容量的芯片,光电共封装设计存在两种形态(Form Factor),每个光电转换模块的交换容量需要达到6.4T或3.2T。如果未来的芯片交换容量进一步提升到102.4T,则每个光电转换模块的交换容量需要翻倍达到12.8T或6.4T。

光电共封装芯片的两种实现方式

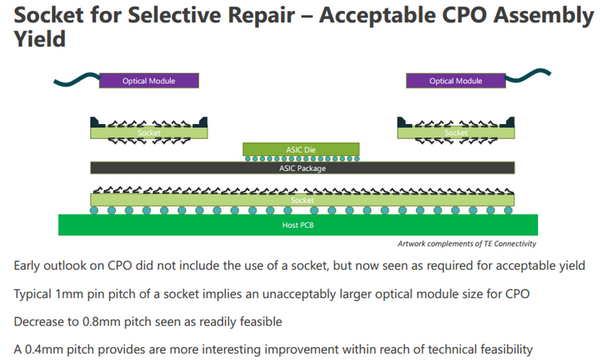

不论光电转换模块的尺寸是大还是小,在芯片基板上都存在通过BGA焊接或Socket连接的安装方式。BGA焊接方式虽然很成熟,但一旦焊接在基板上,出现故障时的更换显然会比较麻烦。通过Socket的方式放置光电转换模块,在维修更换方面会更为容易一些,但需要连接器厂家开发能在芯片基板上使用的小尺寸Socket产品。

光电共封装芯片上的Socket应用

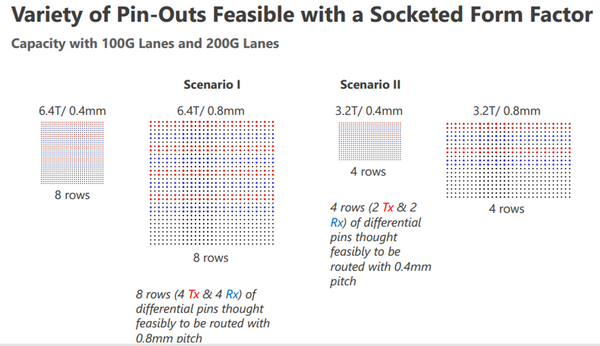

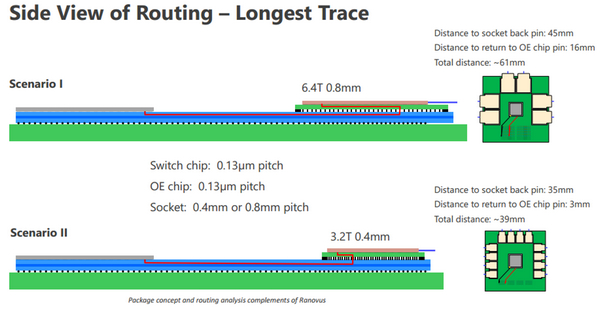

对于这两种尺寸的光电转换模块在基板上的管脚排布方式,目前业界普遍认为有0.4mm和0.8mm两种间距规格可供选择。对于大的光电转换模块,由于管脚数量较多,使用0.8mm间距的焊盘阵列更为合适;对于小的光电转换模块,则可以考虑使用0.4mm间距的焊盘阵列。芯片设计者在选择基板上光电转换模块的管脚间距尺寸时,不仅要考虑加工可实现性,还要考虑基板上信号走线的难易程度。

光电转换模块在基板上不同间距的管脚排布

针对光电转换模块两种尺寸的管脚间距,其与基板上核心Die之间的高速信号链路长度也会不同。根据初步的估计,采用0.4mm管脚间距的小尺寸光电转换模块在芯片基板上的走线长度会更短一些。对于112Gbps和224Gbps信号速率,更短的传输距离不仅意味着更高的信号质量,也意味着更低的能耗。因此,业界目前更倾向于在光电共封装的高密度交换芯片里使用小尺寸的光电转换模块。对于一些密度不是太高的网络或计算类芯片,在芯片基板上使用大尺寸的光电转换模块也是可行的。

光电转换模块不同尺寸管脚间距对应的高速链路长度

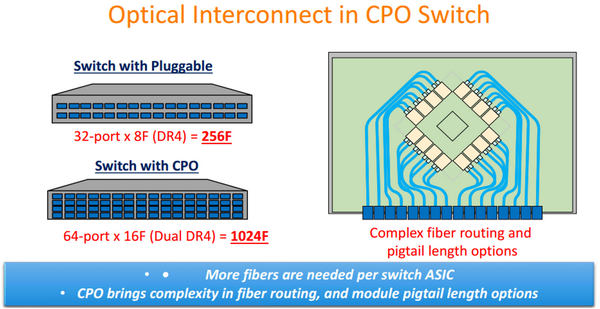

有了光电共封装交换芯片的初步设计方案,使用这种芯片的盒式交换机的系统设计就有了眉目。交换机面板侧的IO形态没有什么大的变化,但IO模块与交换芯片之间的信号连接从PCB上的电信号变为了光纤互连。可以想象一下,打开这种盒式交换机设备的上盖,映入眼帘的将会是一束束纤细的光纤。

使用光电共封装芯片的盒式交换机形态

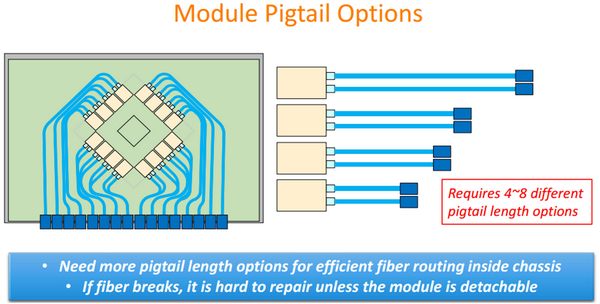

由于交换机上有数量众多的IO端口,设备内部的光纤数量也就不会少。而且由于各个IO模块与光电共封装芯片之间的距离各不相同,这也就使得从芯片上引到IO端口的光纤长度会差异较大。如果光电共封装芯片的外部信号接口引出统一长度的光纤,这不仅会增加芯片的成本,还会增加交换机设备内部光纤布线的复杂度。

光电共封装芯片所需的不同长度光纤

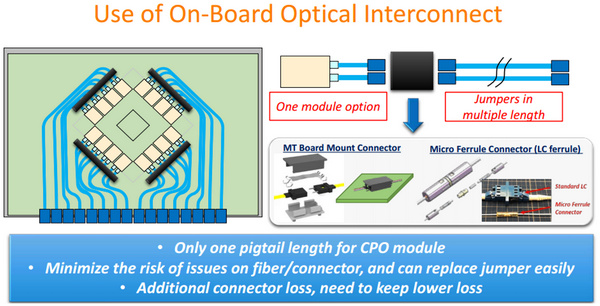

如果光电共封装芯片不直接把光纤引到IO口上,而是在芯片四周放置光纤连接器,那么就可以让光电共封装芯片的外部信号接口全部引出长度相同的光纤。这些从芯片引出的光纤连接到光纤连接器上,经由连接器转接之后,再连接到IO端口上。于是,光电共封装芯片就只需要一种规格,用户只需要采购长度不同的光纤即可。而购买和使用不同长度的光纤,将会降低链路组装的复杂度和成本。

使用板载光连接器的互连方式

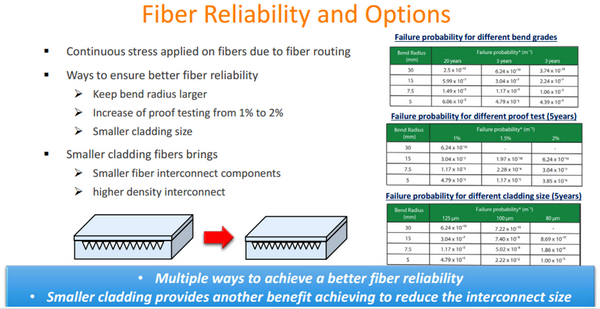

任何一种先进技术,一旦进入到工程实践,就必须要考虑可靠性和可维护性的问题,光电共封装的芯片设计技术也不例外。由于这类芯片会用到大量的光纤进行信号连接,而光纤的弯曲半径、覆盖膜厚度等因素都会影响到光纤的失效率,所以选择哪种类型的光纤、如何取得更高的生产加工良率,都将会是芯片设计者、系统设计者需要仔细考虑的问题。

影响光纤可靠性的因素

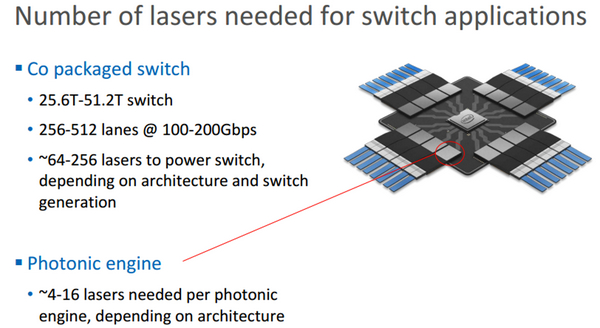

除了光纤的选择之外,在光电共封装芯片的光电转换模块里还存在大量的激光器。按照目前的估计,每一个小的光电转换模块(光引擎)里会有4~16个激光器。这样一来,在光电共封装芯片里就存在一个较大的激光器阵列。

光电共封装交换芯片所需的激光器

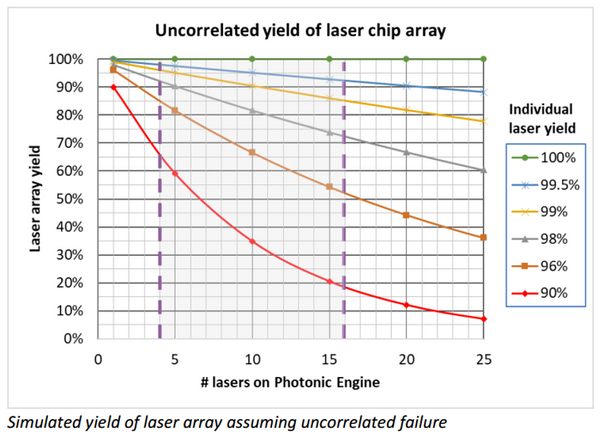

在将每个激光器的良率都看成是与其它激光器不相干的情况下,每个激光器良率的累积就将是整个光引擎的良率。按照理论计算,对于具有4个激光器的光引擎,只有每个激光器的良率达到98%,光引擎的良率才能超过90%。而如果在一个光引擎里有多达16个的激光器,则每个激光器的良率要达到99.5%,光引擎的良率才能超过90%。良率的这些限制对于整个硅光模块生产加工的品质控制提出了很高的要求。

激光器阵列良率的预计变化曲线

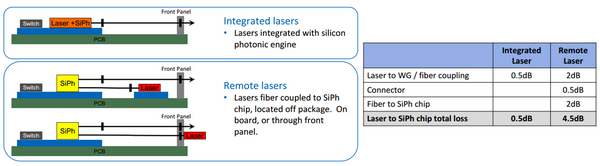

如果把激光器拿到光电共封装芯片的外面,激光器质量的好坏就不会影响到主芯片的良率,这样做还可以有效地降低主芯片的功耗,毕竟众多激光器的功率消耗也不小。但这样做又会带来另外的一个问题,那就是激光器上的光信号与芯片内部硅光模块部分对接时的光耦合损耗。按照目前的预计,将激光器集成到芯片内部,光耦合损耗只有0.5 dB左右。而一旦将激光器拿到芯片外部,光耦合损耗就将增加到4.5 dB左右。对于112Gbps或224Gbps信号速率,是否要增加额外的4 dB信号衰减,是必须要仔细斟酌的事情。

激光器放到主芯片之外带来的光耦合损耗

从以上的探讨中可以看到,先进的光电共封装芯片设计技术虽然对于解决信号速率的提升、芯片带宽容量增加的问题有极大的助力,但需要考虑的工程实践问题也不少。这些工程问题的解决有赖于广大技术人员在未来几年的持续努力。

总 结

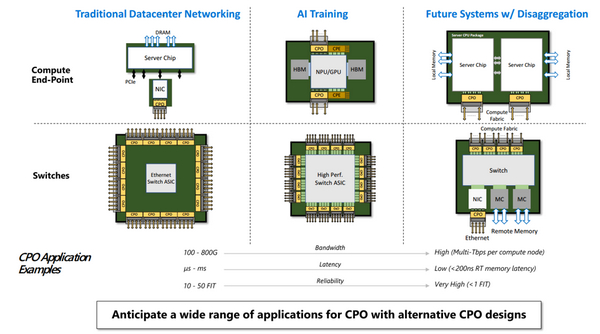

最近这几年,一谈到光电共封装技术,人们往往就会想到其在交换芯片上的应用。其实除了交换芯片之外,光电共封装技术在传统的光模块、GPU等计算类芯片、火热的AI加速计算芯片上都可以得到应用。光电共封装技术的应用不仅会改变芯片设计的方式,也将会改变整机系统的设计方式。

光电共封装技术广泛的应用场合

按照Intel、Broadcom等厂家的预计,光电共封装技术将会在2023~2025年之间得到实际应用,对应的芯片产品到时也会开始逐渐推向市场。虽然距离实际工程应用还有几年的时间,但对于光电共封装技术的深入研究已经刻不容缓了。这也正是OIF等标准组织开始考虑制定针对这类产品国际标准的原因。相信随着标准组织工作的推进,光电共封装技术的落地将会更加有据可循。

本文地址:http://www.iccsz.com//Site/CN/News/2021/02/02/20210202011806623015.htm 转载请保留文章出处

关键字: 光电共封装

文章标题:光电共封装芯片在系统应用中的展望

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1