Multilane针对高速wafer ATE测试方案

ICC讯 MultiLane总部位于黎巴嫩,创立于2006年。MultiLane是数据通信领域高速接口测试和数据中心测试方案的提供商。产品广泛应用于半导体、数通等产品验证测试。作为高速测试行业的领导者,MultiLane将其领先的误码仪和数字采样示波器集成到Advantest 的 V93000 ATE 测试机台,以支持更高速率芯片的测试,高度集成的BERT和DSO提供32个通道的测试能力,最高可达112 Gbps PAM4和35GHz输入带宽。利用这一独特的集成方案,可以进行数字和模拟FT以及CP 测试,包括serdes测试、发射机、放大器、具有高速 I/O 的 ASIC 以及其他有源和无源高速设备。以太网、HDMI、USB 3/4、PCIe5/6、光纤通道等测试都可以支持。BERT 和示波器还可用于 IC 验证、检定和生产测试。

其中针对TIA的CP和FT测试方案,目前已经成功运用于全球领先的TIA芯片制造商产线测试,产线普及率遍及北美,新加坡,马来西亚,台湾。国内也已经有领先的TIA芯片厂商开始引入此方案进行小批量生产测试, ATE自动化测试方案,完美解决了TIA CP测试中探测的难点问题。

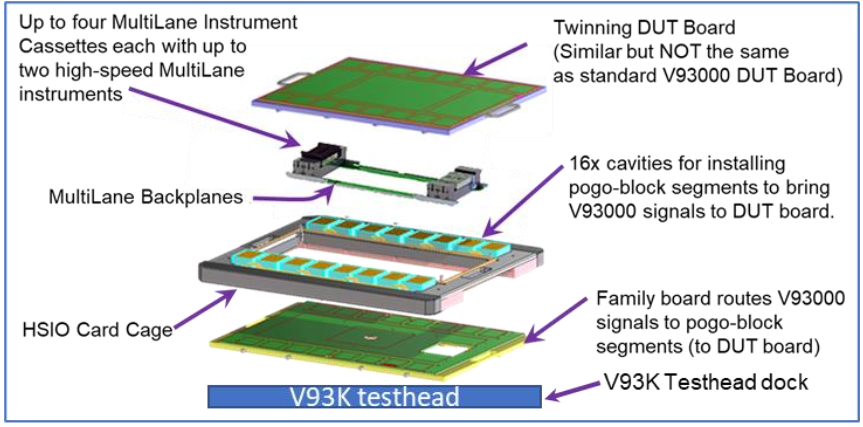

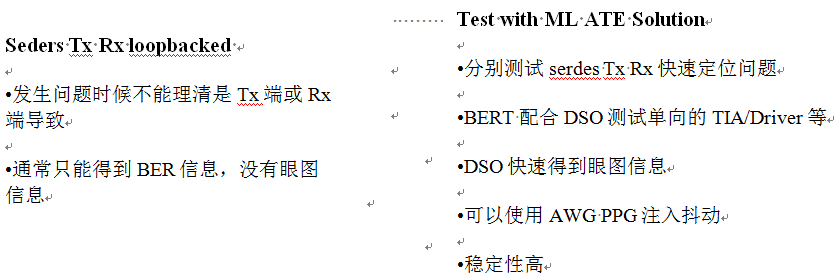

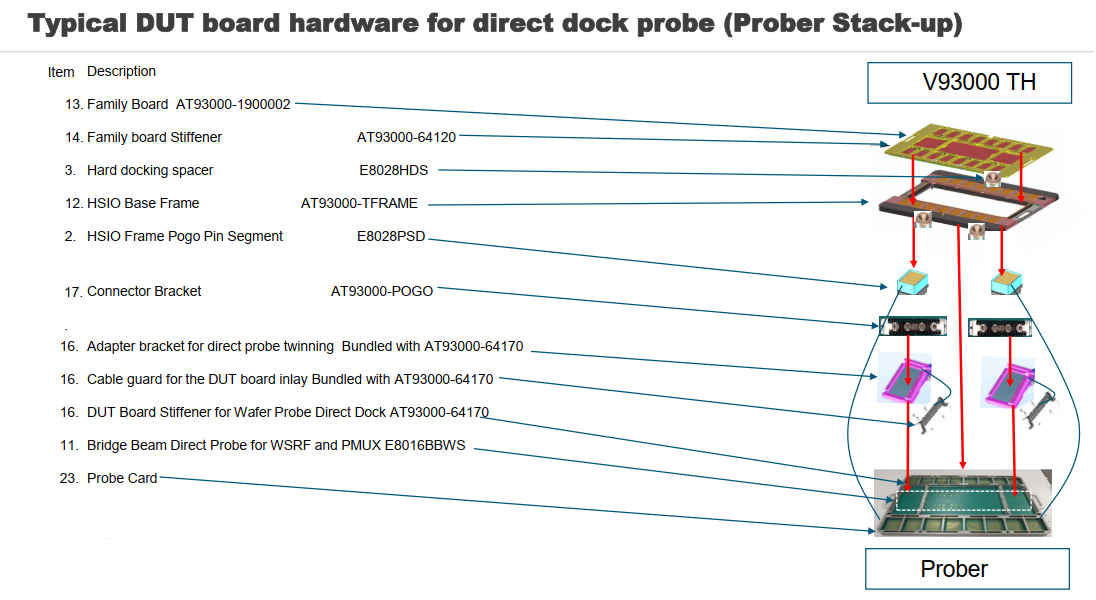

Multilane ATE测试系统主要由Family Board, HSIO Card Cage, ML Instrument Cassettes ,DUT Loadboard 或Probe Card四个部分组成,Family Board 兼容CTH, STH Test Head,并引出93000本身的测试资源。HSIO Card Cage让Pogo Pin通过到达DUT, ML Instrument Cassettes 是高速BERT 或DSO 或AWG仪器,是这套系统的关键。DUT Board根据是FT 或 CP的应用 在Docking方向及细节上稍有不同。Multilane ATE Solution 能够分别对serdes Tx 或 Rx进行测试,快速定位问题。具有覆盖范围广,测试时效高,稳定性高等特点。软件方面 ML Instrument 提供API接口,V93000 Smartest 可以对Instrument进行设置,读取结果等操作。

为更好地服务国内客户,2023年MultiLane Inc 与上海泽丰半导体科技有限公司签署了《战略合作框架协议》。双方本着互惠互利、实现双赢的目标,在平等自愿的前提下就高速ATE测试方案达成战略合作。

DSO 有多种内建的 filters 如 Bessel-Thomson, CTLE, DFE, FFE等,并且可以De-embed, embed 探针及fixture PCB trace等的S参数。能够对信号路径的每个部分分别进行精准的Calibration控制。搭配泽丰性能优异的Probe Card。是wafer级 characterization 及快速产测的理想方案。

关于MultiLane:

MultiLane是数据通信领域高速接口测试和数据中心测试方案的提供商。覆盖到早期的10 G到前沿的800 G以太网,主要产品包括误码仪、任意波形发生器(AWG)、光/电口采样示波器、时域反射计(TDR)、QSFP-DD, OSFP等其他各种封装形式的主机、模块一致性测试夹具、环回模块、适配器与分析仪等。产品广泛应用于半导体、DAC铜缆、AOC光缆、有源线缆、光模块、和交换机产品验证测试。我们的创新步伐紧跟行业快速变化的需求。

同时为帮助行业客户加速产品开发部署进程,Multilane也提供一致性测试服务,信号完整性设计服务等,另外Multilane的高速ATE 模组搭配ATE测试机台,已广泛应用于wafter级的全自动化测试,了解更多信息请访问Multilane官网 www.multilaneinc.com

或咨询中国区销售经理:林瑶 13621907413

本文地址:http://www.iccsz.com//Site/CN/News/2023/05/29/20230529063053395589.htm 转载请保留文章出处

关键字: Multilane wafer ATE 测试方案

文章标题:Multilane针对高速wafer ATE测试方案

2、免责声明,凡本网注明“来源:XXX(非讯石光通讯网)”的作品,均为转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。因可能存在第三方转载无法确定原网地址,若作品内容、版权争议和其它问题,请联系本网,将第一时间删除。

联系方式:讯石光通讯网新闻中心 电话:0755-82960080-168 Right

- · Cox Communications收购Unite Private Networks

- · MultiLane 发布OSFP-XD 评估板

- · S&T Iskratel推出大容量PON OLT

- · Multilane联合多家知名厂商共同助力800G生态测试

- · Adtran与Satelles建立合作关系增强网络的可靠性和安全性

- · OFC 2023:联特和MultiLane利用TFLN技术平台进行800G OSFP的误码率测试现场演示

- · Consolidated押注光纤 放慢扩建速度

- · Seagate Technology部署瞻博网络的AI驱动企业解决方案

- · 诺基亚和Moratelindo升级光传输网络以提高印尼的容量

- · 缺货!华为紧急增产Mate50!

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1