硅光芯片的晶圆级测试

做过光芯片测试的同学应该都深有体会,使用手动耦合平台,一天时间内测试的结构非常有限,效率非常低,更不用提实验中可能还会出现一些幺蛾子。如果硅光芯片开始大批量生产,如此低效率的测试显然需要改善,必须采用高速、有效、可靠的测试方案。这篇笔记整理了一些用于晶圆级测试的方案。

文献1中进行了一个有趣的估算,商用的晶圆级自动化测试设备约200万美元,测试时间1s相当于花费3美分,而一个10mm^2的硅光芯片成本约10美分,因此如果单个芯片测试超过3秒,那么测试的费用就会大于芯片的成本。虽然这种估算方法不一定合理,但是至少说明了测试的重要性。

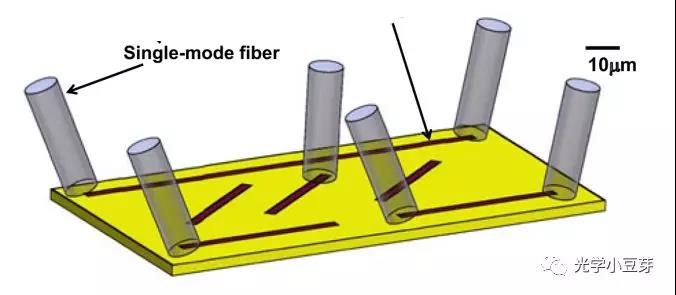

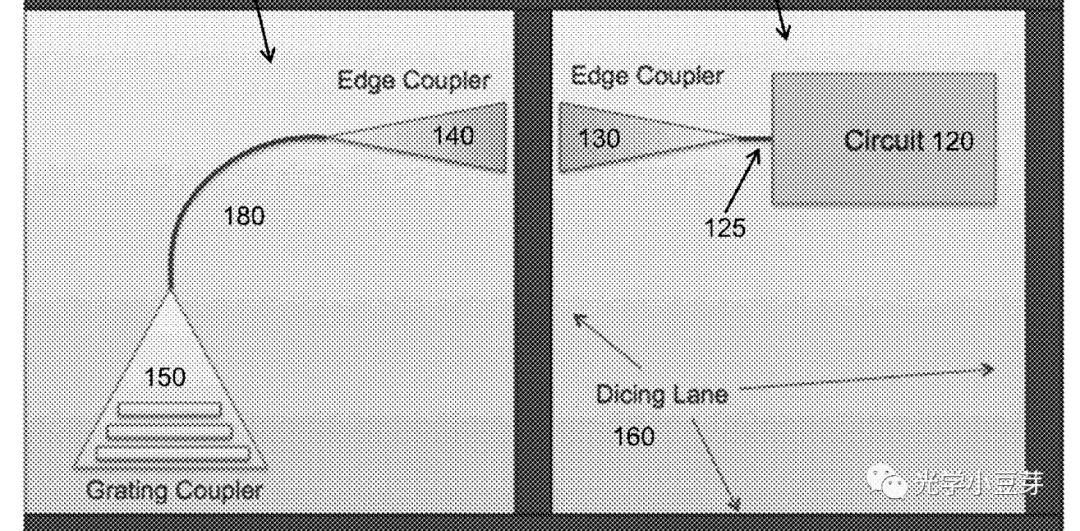

硅光芯片的耦合方案主要分两种,即端面耦合器和光栅耦合器。其中,端面耦合器虽然耦合效率高,带宽大,但是由于其位于芯片的两端,不方便做片上的在线测试。而光栅耦合器比较灵活,可以位于芯片上的任意位置,因而是晶圆级测试的首选,典型的光栅测试结构如下图所示:

(图片来自 https://link.springer.com/chapter/10.1007/978-3-319-42367-8_14)

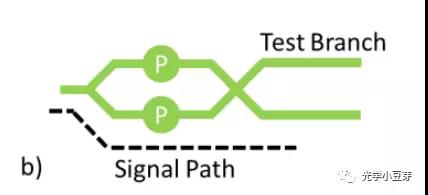

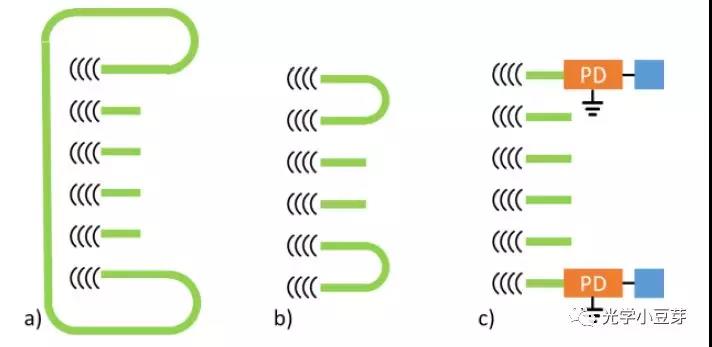

对于一个较复杂的集成光路,为了检验其各个功能单元的性能,通常在特定的位置处添加定向耦合器与光栅耦合器,分出较小比例的光场进行测量。典型的结构如下图所示:

(图片来自文献1)

这种方案比较直接,可用于在功能单元较少的时候。一旦器件数目较多,需测试的结构相应增加,辅助测试的结构就会占据较大的面积。而流片面积直接与成本挂钩。另一方面,假设一个测试结构分光比是5%, 10个测试结构的分光损耗就会达到2.2dB,会影响整个系统的link budget。

为了解决上述的问题,研究人员提出了多种方案,来减小测试结构的影响。

方案1:可擦除的光栅耦合器

该方案利用Ge的离子注入形成光栅耦合器,测试完成后,可通过激光退火的方式擦除该光栅耦合器。Ge的注入导致Si的晶格无序,单晶硅变为非晶硅,而退火后,原子重新有序排列,转变为单晶硅,从而达到了擦除光栅耦合器的目的。下图是擦除前后的结构示意图:

(图片来自文献2)

实验测得的耦合损耗为6.8dB, 比传统光栅耦合器高了2.3dB。退火后的结构仍然存在0.7dB的额外损耗,这一参数还有待提高。

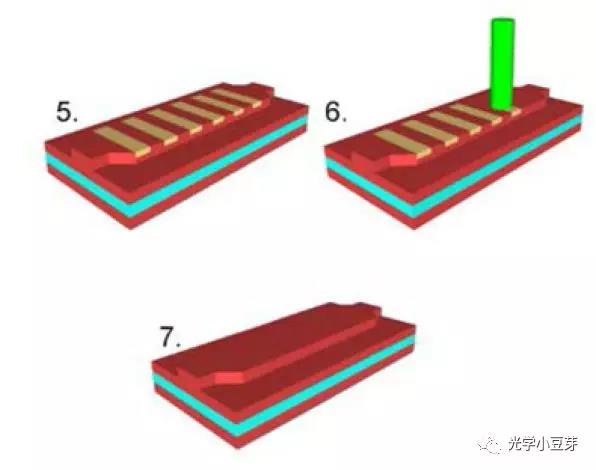

2. 非接触式的电导率监测

该方案采用的电学检测方案,而不是上述的光栅耦合器。其结构如下图所示:

(图片来自文献3)

该方案在待测波导附近制作两个金属电极。将硅波导看成一根导线,由于Si-SiO2界面处存在表面态吸收(surface state absorption),导致波导内的载流子浓度会随着波导内的光强变化而变化。而载流子浓度会影响电导率,利用这两个金属电极测出电导率的变化,进而知晓硅波导内光强的变化。实验时,一个电极与交变电压源相连,另一电极与跨阻放大器相连,用于接收信号。

该方案另辟蹊径,没有直接测试光信号,而是转变为电信号进行测试。制备金属电极不需要额外的工艺流程,并且不会占据太多的面积。但是该方案不能检测高频信号。

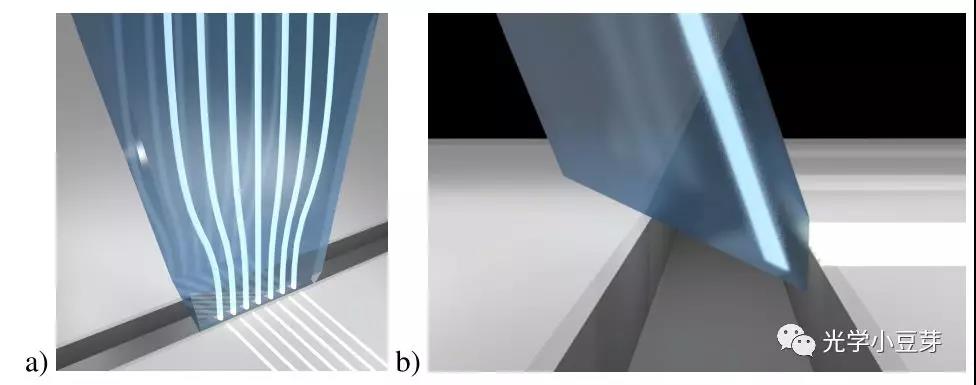

3. 端面斜切的PLC探针

该方案使用端面斜切的PLC芯片。PLC芯片放置于端面的刻蚀槽中,光场在斜切处反射进硅波导中。其结构示意图如下图所示:

(图片来自文献4)

实验中测得的耦合损耗为5.7dB, 相比于单模波导耦合,引入了2.2dB的额外损耗。借助该方案,斜切的PLC芯片作为光学探针(optical probe),可以进行基于端面耦合器的线上测试。

4. 光栅耦合器与端面耦合器共存方案

该方案的结构如下图所示:

(图片来自文献5)

整个芯片分为两部分,左半部分为一个光栅耦合器与端面耦合器相连,右半部分为端面耦合器与集成光路相连。利用光栅耦合器进行线上测试,后续将左半部分划切掉,保留右半部分。

该方案既利用了光栅耦合器线上测试的优势,最终芯片采用端面耦合器,又可以发挥端面耦合器的优点。此外相比于以上其他几种方案,该方案并没有引入新颖的结构,只是在原有基础上将光栅耦合器与端面耦合器进行组合,非常巧妙。

以上是几种晶圆级别的测试方案。个人觉得方案2和4比较好,方案1需要离子注入和激光退火,增加了工艺的复杂度,方案3需要制备专门的PLC芯片。

在集成光路设计中,为了后续方便快速地进行光的耦合测试,通常将I/O端口平行排布,如下图所示:

(图片来自文献1)

晶圆级测试对于降低硅光芯片的成本意义重大,唯有实现快速高效的在线测试,才能提高光芯片的良率。在芯片设计时,也需要考虑到方便后续的测试,两者相辅相成。

参考文献:

1. R. Polster, et.al., "Challenges and solutions for high-volume testing of silicon photonics "

2. R. Topley, et.al., "Locally Erasable Couplers for Optical Device Testing in Silicon on Insulator", Journ. Light. Tech. 32, 2248(2014)

3. F. Morichetti, et.al., "Non-Invasive On-Chip Light Observation by Contactless Waveguide Conductivity Monitoring", IEEE Jour. Sel. Top. Quan. Electron. 20, 8201710(2014)

4. R. Polster, et.al., "Wafer-scale high-density edge coupling for high throughput testing of silicon photonics", OFC 2018

5. Novack, et.al.,"Test systems and methods for chips in wafer scale photonic systems", US patent

本文地址:http://www.iccsz.com//Site/CN/News/2018/05/28/20180528022524163055.htm 转载请保留文章出处

关键字: 硅光

文章标题:硅光芯片的晶圆级测试

※我们诚邀媒体同行合作! 联系方式:讯石光通讯咨询网新闻中心 电话:0755-82960080-168 Right

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备06064786