PCIe3.0光缆设计:光通讯模块搭配控制器

光通讯模块、控制器搭配得宜 PCIe 3.0光纤缆线设计达阵

文/Christopher Wong

对PCIe Express 3.0(PCIe Gen3)机箱间的连接应用来说,光纤技术可提供优于同轴电缆的更佳替代选择。

虽然串行解串行器(SerDes)转换技术原本的设计是在个人计算机(PC)主板上承载PCIe Gen1/Gen2总线讯号,但也可简单应用到同轴电缆上做为数据中心与服务器机箱间的互连接口。不过,铜缆的通道特性将会因PCIe Gen3更高信道频率而大幅度劣化,因此长距离的铜线互连技术将面临无法满足导入8Gbit/s PCIe Gen3技术产品对成本、效能、尺寸与重量的要求。

光纤技术为高信道数PCIe Gen3接口提供非常具有吸引力的替代方案,例如大幅延长的联机距离、更小的尺寸、更轻的重量、更低的功耗、更高的效能,以及更具竞争力的成本。虽然采用光纤的PCIe Gen3互连标准尚在初期制订阶段,但市面上已有做为过渡方案的产品。

本文将介绍PCIe Gen3电气标准,以及将目前商用光纤技术应用到低成本PCIe Gen3的挑战,并将使用由PLX和安华高(Avago)共同开发的解决方案探讨PCIe Gen3光学联机的效能、成本、模块外型、尺寸,以及制造上面临的问题,并提出PCIe Gen3端对端光纤联机的设计架构,描述光纤解决方案如何用来支持商业PCIe应用的全64Gbit/s(双向128Gbit/s)通讯容量。

PCIe Gen3传输速率翻倍成长

PCIe总线是提供中央处理器(CPU)与相关周边,如绘图显示适配器、内存、磁盘驱动器和外部输入输入(I/O)适配卡等连接的高速串行技术,最初由英特尔(Intel)开发,目前已逐渐成为大部分桌面计算机、工作站及高阶服务器的互连标准,同时也逐渐在一些较大型系统中成为被动式背板互连的技术。

在物理层(PHY Layer)上,PCIe以两个端点设备间单一或多个点连接实现,称为通道(Lane),每个通道都由两个低电压交流耦合差动讯号对组成,形成两个联机端点设备间的高速全双工比特流(Bitstream)。比特流中使用8b/10b编码方法嵌入数据频率达到超高数据传输率。为满足更高的容量,PCIe信道可经过组合形成二、四、八及三十二信道的多信道联机,并透过信道传送封包数据。

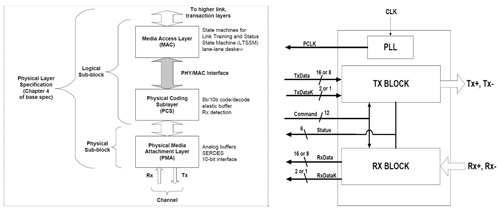

当PCIe Gen1标准于2003年推出时,每个通道的连接速度定义为2.5Gbit/s,所采用的8b/10b线路编码法会降低有效容量20%;PCIe Gen2则将速度加倍为5Gbit/s, 带来三十二通道的PCIe连接器支持,达到高达160Gbit/s的总比特率。图1所示为PCIe Gen1与Gen2物理层功能分工。

图1 PCIe Gen1与Gen2物理层功能分工(左)与方块图(右) 图片来源:英特尔

2010年底定的PCIe Gen3规格则再一次将信道容量加倍,并以称为“打散(Scrambling)”的技术取代Gen1与Gen2使用的8b/10b线路编码方式,可降低信道负担约1.5%。

光纤延伸PCIe接口联机距离

由于PCIe技术的高频讯号须额外利用阻抗受控信道,减低讯号噪声,且联机距离相对较短,因此比较适用于CPU与周边位置接近的连接。

先不论技术上的挑战,业界已对使用电子与光纤缆线延伸PCIe联机到机箱间应用具高度的兴趣。服务器、交换机及储存设备间透过PCIe连接时,并不需中介传输通讯协议或是相关的电子零组件,除可降低系统延迟并提高传输效率外,使用PCIe还具降低整体系统复杂度、成本及耗电的优点。

为支持这些应用,业界也制定外部PCIe(External PCI Express, ePCIe)规格,可将PCIe Gen1的2.5Gbit/s讯号传输延伸到数公尺长的同轴电缆,目前已被应用于包括储存系统、高效能运算计算机,以及其他需要高容量、多机箱系统互连的产品,例如高阶影音系统等。

虽然更快的讯号会因更长的缆线导致衰减、对参考频率抖动更为敏感,以及其他讯号完整性问题限制,无法实现较长的缆线距离,业界目前已针对ePCIe Gen2的缆线规格进行解决方案的开发,而这些问题在PCIe Gen3 8Gbit/s传输速率时,将更加复杂,且需更昂贵的等化与时序解决方案。事实上,光纤是PCIe Gen3芯片与缆线业者研发产品时,要使产品兼具较长联机距离与更高容量弹性设计较佳考虑,促使光纤成为延伸现有PCIe总线到多机箱互连的铜缆替代方案。

值得注意的是,当PCIe Gen3开始量产时,光纤缆线将比铜缆解决方案耗电更少且成本更低,这些特性使采用光纤的PCIe成为目前应用于数据中心连接服务器、交换机及其他储存设备其他传输接口的良好替代方案。在整个输出输入连接使用PCIe还可减少甚至免除通讯协议转换芯片的需求,从而降低整体系统成本、功耗及避免通道延迟的问题。

光纤版PCIe Gen3过渡方案现身

虽然PCIe-SIG发表使用光纤的PCIe Gen3标准还需几年时间,但目前已有商用产品做为过渡方案,使用市面上可取得的PCIe Gen3组件及平行光收发器模块,可大幅加速特定应用光学互连产品的开发,满足无法等待PCIe SIG提出Gen2/Gen3光纤规格的市场。

由于PCIe的媒体访问控制(MAC)与PHY层的接口非常简单并拥有良好的文件说明,因此可非常容易使用市面上现有的PCIe Gen3交换器,或其他端点组件推动平行光收发器模块,而非PCIe Gen3规格中定义的多信道电气SerDes驱动器。对PCIe Gen3最适合的高效能应用,较保险的做法是假设它们需要至少八个平行信道容量。

多通道端点可使用目前市面上多个供货商的产品实现,包括平行光发射/接收模块中的垂直腔表面发射雷射(Vertical Cavity Surface Emitting Laser, VCSEL)数组。采用VCSEL技术的平行光学模块可支持多达十二个平行信道,每信道以8Gbit/s或更高速度运作,并提供150公尺的缆线。

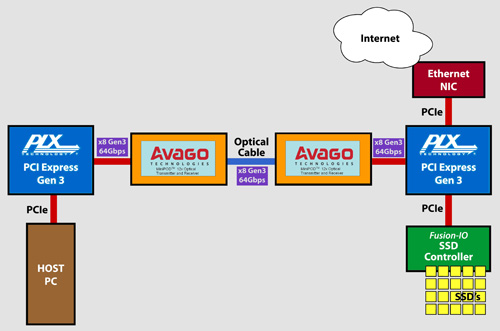

为评估使用商用产品的可行性,本文建立一个概念验证展示系统(图2),由内含四十八通道PCIe Gen3交换器适配卡的主控计算机组成,交换器推动十二信道10Gbit/s MiniPOD光学模块,并使用八个光学信道,另四个则未使用。

图2 概念验证光学PCIe联机展示系统方块图

光学PCIe联机设计挑战多

本文架构概念验证系统的一个主要理由是,提供使用商用零组件做为光学PCIe联机应用的可能性证明。此外,原型系统开发与测试也会找出几个必须解决的问题,特别是在光学领域的PCIe通讯协议支持上,这些问题包括:

· 接收器侦测

平行光收发器模块并未提供由PCIe发射器用来侦测联机存在的50奥姆(Ω)阻抗电气界面。当适当的负载存在时,发射器会触发,并以在组件接收端所侦测到的模式运作,特别的是,它会做为开始传送一系列线路探查讯号的队列,以便让接收器计算并做为等化电路设定的参考,在使用标准PCIe MAC组件支持光学联机的应用中,发射器线路探查与等化功能必须被关闭。

·电气待机模式

PCIe电气接口包含在无数据传输时将联机变成节能待机(Electrical IDLE, EIDLE)模式的功能,不过采用光纤联机时这个模式可能会造成问题,原因是收发器较长的暖机时间可能会产生线路跳动或不适当的偏压,带来错误的EIDLE侦测或跳离EIDLE状态。

·频率

由于大部分光学PCIe联机并不会在相同机架间有两端点的连接,因此本文须假设它们不会使用相同的重置或系统频率讯号,在这些应用及本篇文章提供的范例中,并无法在联机上实现同步重置或频率,因此端点必须能够支持异步频率运作。

· 远程重置

在大部分应用中,PCIe联机的远程光学适配卡会在主系统前供电,因此远程电路卡在设计上须能在电源启动时进行自动重置程序,以便在主控端启动时能完全初始化并开始进行联机。另一个做法是若操作系统能完全由用户控制,那么系统就能以任何顺序启动,虽然这种方式并不常见,但对客制化应用软件在系统中定时检查联机状态非常需要,在这样的组态下,在两方系统确认完成传输准备后,操作系统便可启动标准的系统列举与程序动作。

·外部讯号

目前针对同轴电缆定义的PCIe外部缆线规格,存在光学解决方案无法承载的额外讯号,例如100MHz的缆线参考频率(RefClk)并不需要,原因是频率可由PCIe收发器的资料串流中取得。此外包括SB_RTN单端边频带讯号的回返电气讯号接脚、CPRSNT#安装的缆线/下传子系统上电、CPWRON上传子系统电源稳定通知、CWAKE#唤醒事件的电源管理讯号,以及CPERST缆线PERST#缆线平台重置等接脚,在使用光纤缆线时也无法使用。

选择支持八信道组态组件

许多标准完成前的开发动作须实现商用产品尚未提供的功能,通常以使用现场可编程门阵列(FPGA)及离散组件达成。不过在PCIe Gen3的例子上,市场上已有实现概念验证系统所需功能的产品,虽然它们并没有针对这类特殊应用优化。

选择最适合的光学模块予本文测试应用范例,将包含几个考虑,包括信道数量、外型规格及兼容性等。虽然PCIe规格允许二、四、八、十二及十六个信道,但光学模块通常以八或十二个通道组态提供,本文选择八通道组态的原因是其经常使用于高效能PCIe 2.0的设计中,预计也会在PCIe Gen3标准受到欢迎。此外,标准化八信道PCIe端点产品也给设计团队带来丰富的组件选择,其中,由于CXP与MiniPOD模块容易取得并拥有良好的效能特性,因此成为两个最具吸引力的选择。

MiniPOD模块机械设计较佳

本文选择MiniPOD的原因是其嵌入式平行光学组态可直接安装到印刷电路板上,带来更好的电气与机械设计。MiniPOD光学模块的占用面积为18.6毫米(mm)×22毫米,并且可接受十二通道的扁平缆线或圆形缆线。扁平缆线的优点包括厚度低及模块可紧密堆栈;圆型缆线则提供更好的稳固度及更高弹性的弯折,图3为透过扁平缆线耦合并使用业界标准MTP连接器MiniPOD光学模块。

图3 十二信道嵌入式平行光纤收发模块MiniPOD

和CXP模块使用的电路板边缘安装不同,MiniPOD光学模块可简单安排在电路板中央,并提供高速驱动器连接,将承载8Gbit/s电气讯号的电路板走线长度减到5吋,进而可将因电容表面效应造成的耗损与失真控制在最低。边缘安装解决方案的光学或电气PCIe缆线可能达到12~20吋,或更长的走线长度,且还需特殊的电路板材料、发射器去强调、接受器等化及频率数据回复(CDR)等技术解决讯号完整性问题。

本文范例选择四十八信道PCIe Gen3交换器做为两个端点的PCIe控制器,原因是该组件整合用来支持光学领域运作的功能,此交换器可解决的问题,第一为交换器拥有关闭接收器侦测的功能,免除光学缆线提供50Ω阻抗的需求,在此模式,交换器透过对输入数据串流译码进行速度协商。

PCIe控制器第二个解决的问题是EIDLE,原因是该组件能被设定为忽略可能引发电气待机状态的数据串流变化,在此模式下,PCIe控制器持续追踪提供对连接速度协商要求的特定数据符号,因此光学联机能进行列举及联机情况、信道和速度信息的通讯,达到完全运作带宽。

不过由于此交换器经过修改的EIDLE功能无法允许进入或跳出动态电源管理(Active State Power Management, ASPM)状态,因此还是存在一个小问题,但可透过实体上解除并重新启动动作连接来初始化联机的维持能力加以解决,然而缓存器管理,如资源重新配置、BAR编程、端点的可能注册重新编程及讯息遮蔽等就需另外的处理程序。

第三个可由PCIe控制器解决的问题是,交换器支持数据回复用的异步频率模式,允许PCIe光学联机的两端能够独立运作。不过这个异步模式将不支持用来降低印刷电路板上承载PCIe讯号走线辐射电磁干扰的系统展频频率(Spread Spectrum Clocking, SSC)。

利用收发器/光纤控制器实作光纤版PCIe

本文提出的概念验证展示的电路板(图4)包含内建四十八通道PCIe Gen3交换器适配卡的主控计算机,以及一个搭配交换器的光发射器与接收器模块子板,在光学联机的另一端,另一个包含光收发器与接收器模块的交换器接口卡位于电路板上,藉以提供快速周边,如固态硬盘驱动及以太网络(Ethernet)HBA卡的输出与数据整合。

图4 搭配MiniPOD模块的适配卡

实体联机的每一端都使用PCIe Gen3交换器芯片进行终端,包含频率/数据回复以及每个高速端口的发射/接收等化。由于交换器芯片的收发器选用异步模式运作,因此在光学模块中并不须进行频率与数据回复,可进一步保留PCIe的低延迟优势。MiniPOD光学模块在电路板中央位置的设计,电路板走线较短,也可让交换器芯片的Tx与Rx讯号直接与光学模块介接,因此只须在两者间加入交流耦合。

实现30公尺光纤PCIe Gen3缆线

上述的实作电路板成功实现在OM3的低成本多模光纤上,实现超过30公尺的PCIe Gen3八通道缆线。这个光纤缆线支持异步运作(无原生SSC,但提供SSC隔离)、仅L0动作状态(受控操作系统的联机启动与结束控制)、PCIe普通连接速度协商与PCIe标准联机宽度安排功能。

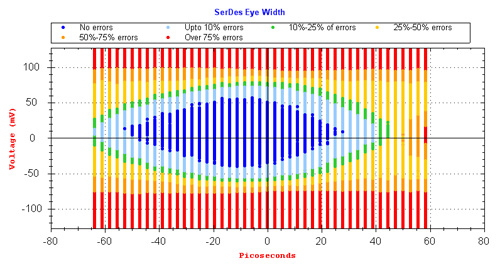

但碍于先前所讨论的技术问题,此一光纤缆线目前并无法具备PCIe动态电源管理、带内同步重置(仅支持带外独立重置)功能。由图5眼图可说明接收器驱动30公尺缆线时,拥有良好的讯号完整性及无错误的数据回复。

图5 PCIe Gen3交换器在30公尺光纤数据传输眼图

在本文实作范例中,MiniPOD光学模块可支持PCIe Gen3以每信道8.0Gbit/s的速度运作,但实际上可支持1G?10.3125 Gbit/s的宽广传输速率,因此这些光学组件可在5.0Gbit/s的PCIe Gen2及2.5Gbit/s的PCIe Gen1运作,不须更改组态也不会牺牲效能。此一传输速率范围不仅可让工程师加速实现PCIe Gen3光纤缆线连接,也可做为未来特定应用产品多重速率光学联机向后兼容的基础。

(本文作者任职于安华高)

本文地址:http://www.iccsz.com//Site/CN/News/2014/01/09/20140109070549570600.htm 转载请保留文章出处

关键字: PCIe 3.0

文章标题:PCIe3.0光缆设计:光通讯模块搭配控制器

※我们诚邀媒体同行合作! 联系方式:讯石光通讯咨询网新闻中心 电话:0755-82960080-188 debison

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183