英特尔演示116 GbpsPAM4收发器测试芯片

ICC讯(编译:Aiur) 根据英特尔近期的一篇博客,文章作者Steven Leibson介绍了英特尔公司的一款采用PAM4调制,以116 Gbps高速运行的长距离收发器测试芯片。这款收发器测试芯片搭载了英特尔10 nm制程技术,兼容CEI-112G-LR-PAM4规范定义的最高速率。测试芯片的116 Gbps运行速率展现了高速收发器设计对当前100/200/400 GbE标准增加容限(margin)的作用,可以支持最新协议和前向纠错(FEC)标准。

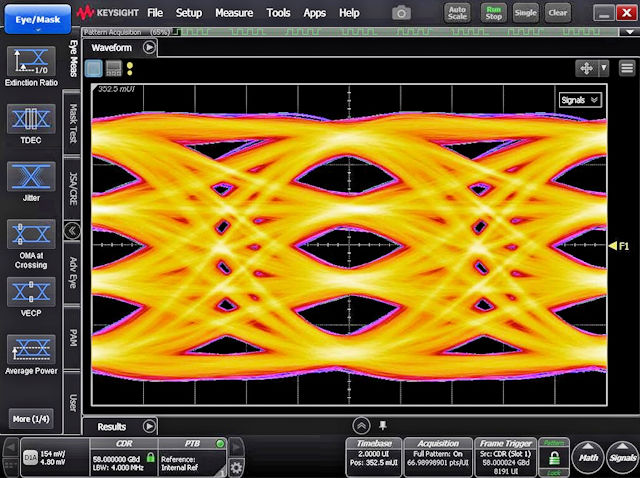

该测试芯片试验已经上传到Youtube视频,视频里介绍这款收发器芯片的发射机通过片上互联和外部布线,将116 Gbps PRBS31码数据传输到同个芯片上的接收机,芯片上从BGA球到BGA球之间的总体插损大于35dB。在测试中,在116 Gbps速率运行时,收发器芯片的性能也超过CEI-112G-LR-PAM4规范的误码(BER)要求将近三个数量级。下图是使用示波器(Keysight采样示波器N1000A + N1060A)测量收发器芯片发射机在116 Gbps工作速率时的嵌入式PAM4眼图。

收发器芯片的发射机以116 Gbps速率运行时的I/O嵌入测量PAM4眼图

用于这款芯片的高速、长距离,基于数字ADC和DAC的收发器架构,以及经过加固的100/200/400 GbE协议栈,将被整合到英特尔®Agilex?I系列FPGA产品组合中,该系列FPGA已针对高容量进行了优化,针对云、企业和边缘应用等高速、带宽密集型网络。

以下为116 Gbps PAM4收发器I/O 芯片演示视频链接

英特尔博客

是德科技公众号

https://mp.weixin.qq.com/s/OAhIAxU9qXz7tuQ2gO5a4w

本文地址:http://www.iccsz.com//Site/CN/News/2020/04/10/20200410091618482658.htm 转载请保留文章出处

关键字: 英特尔

文章标题:英特尔演示116 GbpsPAM4收发器测试芯片

※我们诚邀媒体同行合作! 联系方式:讯石光通讯咨询网新闻中心 电话:0755-82960080-168 Right

- · MaxLinear以1.5亿美元收购英特尔家庭连接部门

- · DARPA PIPES项目展示光学互连成果,光信号接口代替了传统电子I/O,实现传输距离和效率的大幅提升

- · 华为公布搭载英特尔Cascade Lake Refresh处理器的服务器

- · 英特尔展示业界首个一体封装光学以太网交换机

- · 英特尔预测:2024年前全球将建立600万座5G无线基地台

- · 英特尔为5G网络基础设施发布全新软硬件产品组合

- · 英特尔商谈出售家庭连接部门给MaxLinear

- · 英特尔宣布因疫情退出巴塞罗那世界移动通信大会

- · 英特尔因出售5G基带业务导致450人失业

- · 英特尔斥资20亿美元 收购以色列AI芯片初创公司

- 设置首页 | 光通讯招聘 | 企业搜索库 | 广告服务 | 联系我们 | 保护私隐 | 公司介绍

Copyright ? 2009 ICCSZ.com Inc. All Rights Reserved. 讯石公司 www.iccsz.com版权所有 粤ICP备12008183号-1